US007542019B2

(12) **United States Patent**

Park et al.

(10) **Patent No.:** US 7,542,019 B2

(45) **Date of Patent:** Jun. 2, 2009

(54) **LIGHT EMITTING DISPLAY**

(75) Inventors: **Sung Cheon Park**, Suwon (KR); **Won Kyu Kwak**, Seongnam (KR)

(73) Assignee: **Samsung Mobile Display Co., Ltd.**, Yongin (KR)

(\*) Notice: Subject to any disclaimer, the term of this patent is extended or adjusted under 35 U.S.C. 154(b) by 626 days.

(21) Appl. No.: 11/274,041

(22) Filed: Nov. 14, 2005

(65) **Prior Publication Data**

US 2006/0125807 A1 Jun. 15, 2006

(30) **Foreign Application Priority Data**

Nov. 22, 2004 (KR) ..... 10-2004-0095979

Nov. 22, 2004 (KR) ..... 10-2004-0095980

(51) **Int. Cl.**

**G09G 3/32** (2006.01)

(52) **U.S. Cl.** ..... 345/82; 345/205

(58) **Field of Classification Search** ..... 345/82,

345/205, 206

See application file for complete search history.

(56) **References Cited**

U.S. PATENT DOCUMENTS

5,952,789 A \* 9/1999 Stewart et al. ..... 315/169.4

6,323,598 B1 11/2001 Guthrie et al.

6,421,033 B1 7/2002 Williams et al.

6,919,681 B2 7/2005 Cok et al.

2002/0021293 A1 2/2002 Tam

2002/0109457 A1 8/2002 Duineveld et al.

2003/0214469 A1 \* 11/2003 Kageyama et al. ..... 345/82

2004/0070557 A1 4/2004 Asano et al.

2005/0024305 A1 \* 2/2005 Park ..... 345/82

2005/0062696 A1 \* 3/2005 Lo ..... 345/82

2005/0093791 A1 5/2005 Lo

2006/0097965 A1 5/2006 Deane et al.

FOREIGN PATENT DOCUMENTS

JP 2002-215096 7/2002

OTHER PUBLICATIONS

Patent Abstracts of Japan, Publication No. 2002-215096; Publication Date Jul. 31, 2002; in the name of Kwon.

(Continued)

Primary Examiner—Richard Hjerpe

Assistant Examiner—Shaheda A Abdin

(74) Attorney, Agent, or Firm—Christie, Parker & Hale, LLP

(57) **ABSTRACT**

A light display includes scan lines arranged in a row direction to transmit scan signals, a data line arranged in a column direction to transmit a data signal, an image display unit including emission control lines arranged in the row direction to transmit emission control signals, and a pixel in a region defined by the scan lines and the data line. The pixel has a driving circuit for receiving the signals, the data signal, the emission control signals, and a power to drive a current, a switching circuit connected with the driving circuit to receive the current, the switching circuit for selectively applying the current in accordance with the emission control signals, and organic light emitting diodes (OLEDs) positioned on different rows of the image display unit and connected with the switching circuit to receive the current in accordance with an operation of the switching circuit and to emit light.

30 Claims, 15 Drawing Sheets

**US 7,542,019 B2**

Page 2

---

OTHER PUBLICATIONS

SIPO Office action dated Sep. 21, 2007, for corresponding Chinese Application 2005101268174, with English translation, indicating relevance of listed U.S. Appl. No. 6,421,033 and U.S. Publication 2004/0070557 in this IDS.

U.S. Office action dated Dec. 1, 2008, for related U.S. Appl. No. 11/274,062, indicating relevance of remaining listed U.S. references in this IDS.

Patent Abstracts of Japan, Publication No. 2003-043999, dated Feb. 14, 2003, in the name of Suzuki.

\* cited by examiner

FIG. 1

(PRIOR ART)

FIG. 2

FIG. 3

FIG. 4

FIG. 5

FIG. 6

FIG. 7

FIG. 8A

FIG. 8B

FIG. 9

FIG. 10

FIG. 11

FIG. 12

FIG. 13

FIG. 14

FIG. 15

FIG. 16A

R G

<1<sup>st</sup> SUB FIELD>

FIG. 16C

R G

<3<sup>rd</sup> SUB FIELD>

FIG. 16B

R G

<2<sup>nd</sup> SUB FIELD>

FIG. 16D

R G

<4<sup>th</sup> SUB FIELD>

**LIGHT EMITTING DISPLAY****CROSS-REFERENCE TO RELATED APPLICATIONS**

This application claims priority to and the benefit of Korean Patent Application Nos. 10-2004-95979 and 10-2004-95980, filed on Nov. 22, 2004, in the Korean Intellectual Property Office, the entire contents of which are incorporated herein by reference.

**BACKGROUND****1. Field of the Invention**

The present invention relates to a light emitting display, and more particularly, to a light emitting display capable of compensating for threshold voltages of transistors and capable of having a plurality of organic light emitting diodes (OLED) that emit light through one pixel circuit.

**2. Discussion of Related Art**

Recently, various flat panel displays having weight and volume less than comparable cathode ray tube (CRT) displays have been developed. In particular, light emitting displays having high luminous efficiency, high brightness, wide view angle, and high response speed are in the limelight

An organic light emitting diode (OLED) has a structure in which an emission layer that is a thin film for emitting light is positioned between a cathode electrode and an anode electrode. Electrons and holes are injected into the emission layer so that they can be re-combined to generate exciters that emit light when their energies are reduced.

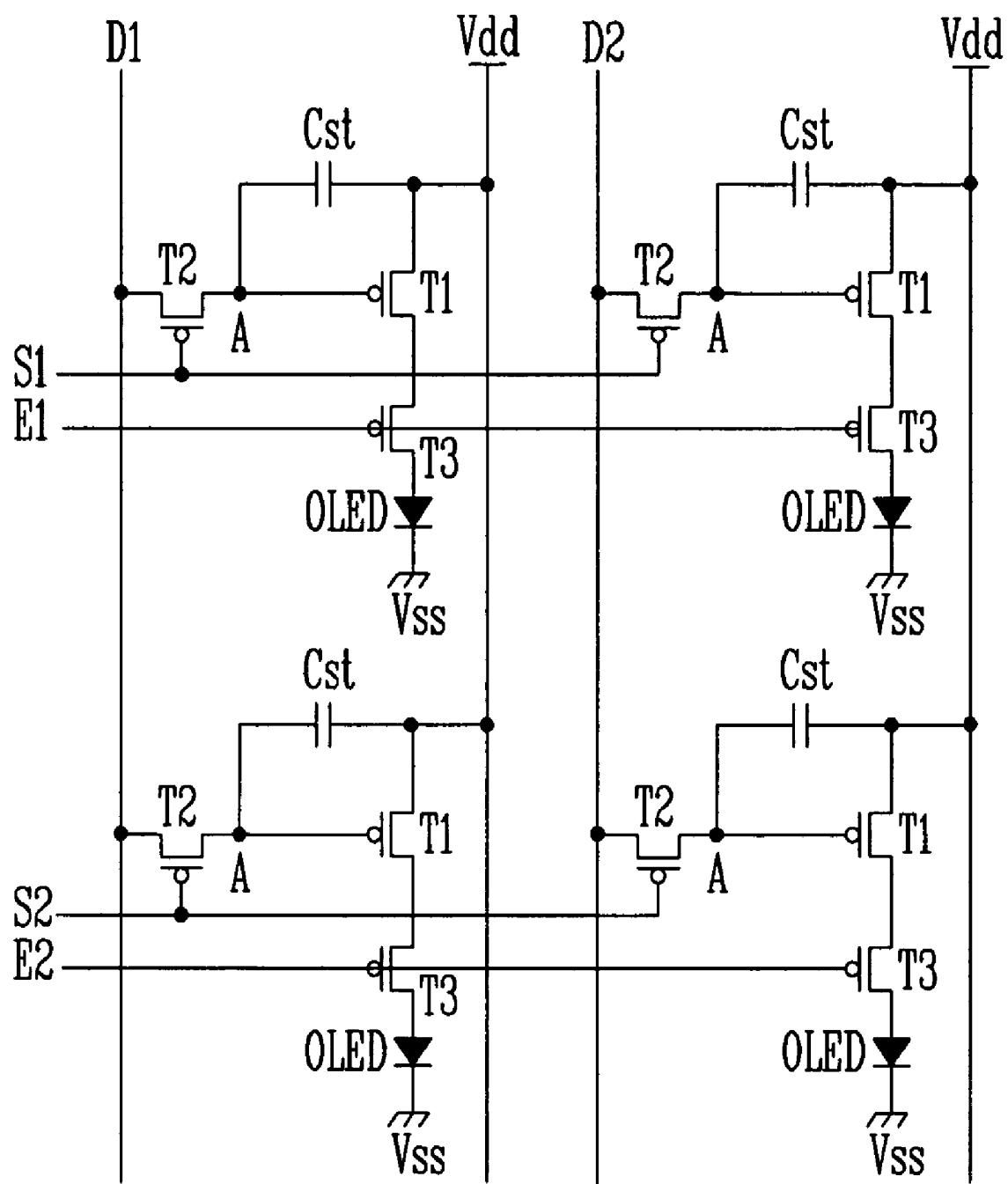

FIG. 1 illustrates a structure of a part of a conventional light emitting display. Referring to FIG. 1, four pixels are adjacent to each other and each pixel includes an OLED and a pixel circuit. The pixel circuit includes a first transistor T1, a second transistor T2, a third transistor T3, and a capacitor Cst. Each of the first, second, and third transistors T1, T2, and T3 includes a gate, a source, and a drain; and the capacitor Cst includes a first electrode and a second electrode.

Since the pixels have the same structure, only the pixel on the left top will be described in more detail. The source of the first transistor T1 is connected with a power source Vdd, the drain of the first transistor T1 is connected with the source of the third transistor T3, and the gate of the first transistor T1 is connected with a node A. The node A is connected with the drain of the second transistor T2. The first transistor T1 supplies a current corresponding to a data signal to the OLED.

The source of the second transistor T2 is connected with a data line D1, the drain of the second transistor T2 is connected with the node A, and the gate of the second transistor T2 is connected with a scan line S1. The second transistor T2 applies a data signal to the node A in accordance with a scan signal applied to the gate thereof.

The source of the third transistor T3 is connected with the drain of the first transistor T1, the drain of the third transistor T3 is connected with an anode electrode of the OLED, and the gate of the third transistor T3 is connected with an emission control line E1 to respond to an emission control signal. Therefore, the third transistor T3 controls the flow of a current that flows from the first transistor T1 to the OLED in accordance with the emission control signal to control emission of the OLED.

The first electrode of the capacitor Cst is connected with the power source Vdd, and the second electrode of the capacitor Cst is connected with the node A. The capacitor Cst stores charges in accordance with the data signal and applies a signal

to the gate of the first transistor T1 by the stored charges for one frame so that the operation of the first transistor T1 is maintained for one frame.

However, according to the pixel used for the conventional light emitting display, since one OLED is connected with one pixel circuit, a plurality of pixel circuits are needed in order to emit light from a plurality of OLEDs so that a large number of the pixel circuits are needed.

Also, since one emission control line needs to be connected with a pixel row, the aperture ratio of the light emitting display deteriorates due to the emission control line.

**SUMMARY OF THE INVENTION**

Accordingly, an embodiment of the present invention provides a pixel and a light emitting display using the same, in which threshold voltages of transistors are compensated so that a uniform current for uniform brightness flows to an organic light emitting diode (OLED) in spite of a deviation in the threshold voltages. An embodiment of the present invention provides a plurality of OLEDs and a light emitting display using the same that emit light through one pixel circuit so that the embodiment can reduce the number of pixel circuits of the light emitting display, the number of data lines, and the number of pixel power source lines, to reduce the size of a data driving part, and to thus improve aperture ratio. An embodiment of the present invention provides a pixel and a light emitting display using the same capable of controlling points of emission time of a plurality of the OLEDs to minimize color breakup.

One embodiment of the present invention provides a light emitting display having first and second scan lines arranged in a row direction to transmit first and second scan signals, a data line arranged in a column direction to transmit a data signal, an image display unit including first and second emission control lines arranged in the row direction to transmit first and second emission control signals, respectively, and a pixel formed in a region defined by the first and second scan lines and the data line. The pixel has a driving circuit for receiving the first and second scan signals, the data signal, the first and second emission control signals, and a first power of a first power source to drive a current, a switching circuit connected with the driving circuit to receive the current, the switching circuit for selectively applying the current in accordance with the first and second emission control signals, and first and second organic light emitting diodes (OLEDs) positioned on two different rows of the image display unit and connected with the switching circuit to receive the current in accordance with an operation of the switching circuit and to emit light. The driving circuit has a first transistor for receiving the first power of the first power source and for supplying the current to the first and second OLEDs, the current corresponding to a voltage applied to a gate of the first transistor, a second transistor for selectively applying the data signal to a first electrode of the first transistor in accordance with the first scan signal, a third transistor for selectively forming an electrical connection between a second electrode of the first transistor and the gate of the first transistor in accordance with the first scan signal, a capacitor for storing the voltage applied to the gate of the first transistor while the data signal is applied to the first electrode of the first transistor and for maintaining the stored voltage at the gate of the first transistor for a predetermined time period when at least one the first and second OLEDs emits light, a fourth transistor for selectively applying an initializing signal to the capacitor in accordance with the second scan signal, a fifth transistor for selectively applying the first power of the first power source to the first

transistor in accordance with the first emission control signal, and a sixth transistor for selectively applying the first power source to the first transistor in accordance with the second emission control signal.

One embodiment of the present invention provides a light emitting display having first and second scan lines arranged in a row direction to transmit first and second scan signals, a data line arranged in a column direction to transmit a data signal, an image display unit including first and second emission control lines arranged in the row direction to transmit first and second emission control signals, respectively, and a pixel formed in a region defined by the first and second scan lines and the data line. The pixel has a driving circuit for receiving the first and second scan signals, the data signal, the first and second emission control signals, and the first power of a first power source to drive a current, a switching circuit connected with the driving circuit to receive the current, the switching circuit for selectively applying the current in accordance with the first and second emission control signals, and first and second organic light emitting diodes OLEDs positioned on two different rows of the image display unit and connected with the switching circuit to receive the current in accordance with an operation of the switching circuit and to emit light. The driving circuit has a first transistor having first and second electrodes connected with first and second nodes, respectively, and having a third electrode connected with a third node, a second transistor having first and second electrodes connected with the data line and the second node, respectively, and having a third electrode connected with the first scan line, a third transistor having first and second electrodes connected with the first and third nodes, respectively, and having a third electrode connected with the first scan line, a fourth transistor having first and second electrodes connected with the third node and an initializing signal line, respectively, and having a third electrode connected with the second scan line, and a capacitor having a first electrode connected with the first power source and a second electrode connected with the third node, a fifth transistor having first and second electrodes connected with the second node and the first power source, respectively, and having a third electrode connected with the first emission control line, and a sixth transistor having first and second electrodes connected with the second node and the first power source, respectively, and having a third electrode connected with the second emission control line.

One embodiment of the present invention provides a light emitting display having first and second scan lines arranged in a row direction to transmit first and second scan signals, a data line arranged in a column direction to transmit a data signal, an image display unit including first and second emission control lines arranged in the row direction to transmit first and second emission control signals, respectively, and a pixel formed in a region defined by the first and second scan lines and the data line. The pixel has a driving circuit for receiving the first and second scan signals, the data signal, the first and second emission control signals, and the first power of a first power source to drive a current, a switching circuit connected with the driving circuit to receive the current, the switching circuit for selectively applying the current in accordance with the first and second emission control signals, and first and second organic light emitting diodes OLEDs positioned on two different rows of the image display unit and connected with the switching circuit to receive the current in accordance with an operation of the switching circuit and to emit light. The driving circuit has a first transistor having first and second electrodes connected with first and second nodes, respectively, and having a third electrode connected with a third node, a second transistor having first and second electrodes connected with the data line and the second node, respectively, and having a third electrode connected with the first scan line, a third transistor having first and second electrodes connected with the first and third nodes, respectively, and having a third electrode connected with the first scan line, a fourth transistor having first and second electrodes connected with the third node and an initializing signal line, respectively, and having a third electrode connected with the second scan line, and a capacitor having a first electrode connected with the first power source and a second electrode connected with the third node, a fifth transistor having first and second electrodes connected with the second node and the first power source, respectively, and having a third electrode connected with the first emission control line, and a sixth transistor having first and second electrodes connected with the second node and the first power source, respectively, and having a third electrode connected with the second emission control line.

node, a second transistor having first and second electrodes connected with a data line and the first node, respectively, and having a third electrode connected with the first scan line, a third transistor having first and second electrodes connected with the second and third nodes, respectively, and having a third electrode connected with the first scan line, a fourth transistor having first and second electrodes connected with the third node and an initializing signal line, respectively, and having a third electrode connected with a second scan line, and a capacitor having a first electrode connected with the first power source and a second electrode connected with the third node, a fifth transistor having first and second electrodes connected with the second node and the first power source, respectively, and having a third electrode connected with the first emission control line, and a sixth transistor having first and second electrodes connected with the second node and the first power source, respectively, and having a third electrode connected with the second emission control line.

#### BRIEF DESCRIPTION OF THE DRAWINGS

The accompanying drawings, together with the specification, illustrate exemplary embodiments of the present invention, and, together with the description, serve to explain the principles of the present invention.

FIG. 1 illustrates a structure of a part of a conventional light emitting display;

FIG. 2 illustrates a structure of a light emitting display of a first embodiment of the present invention;

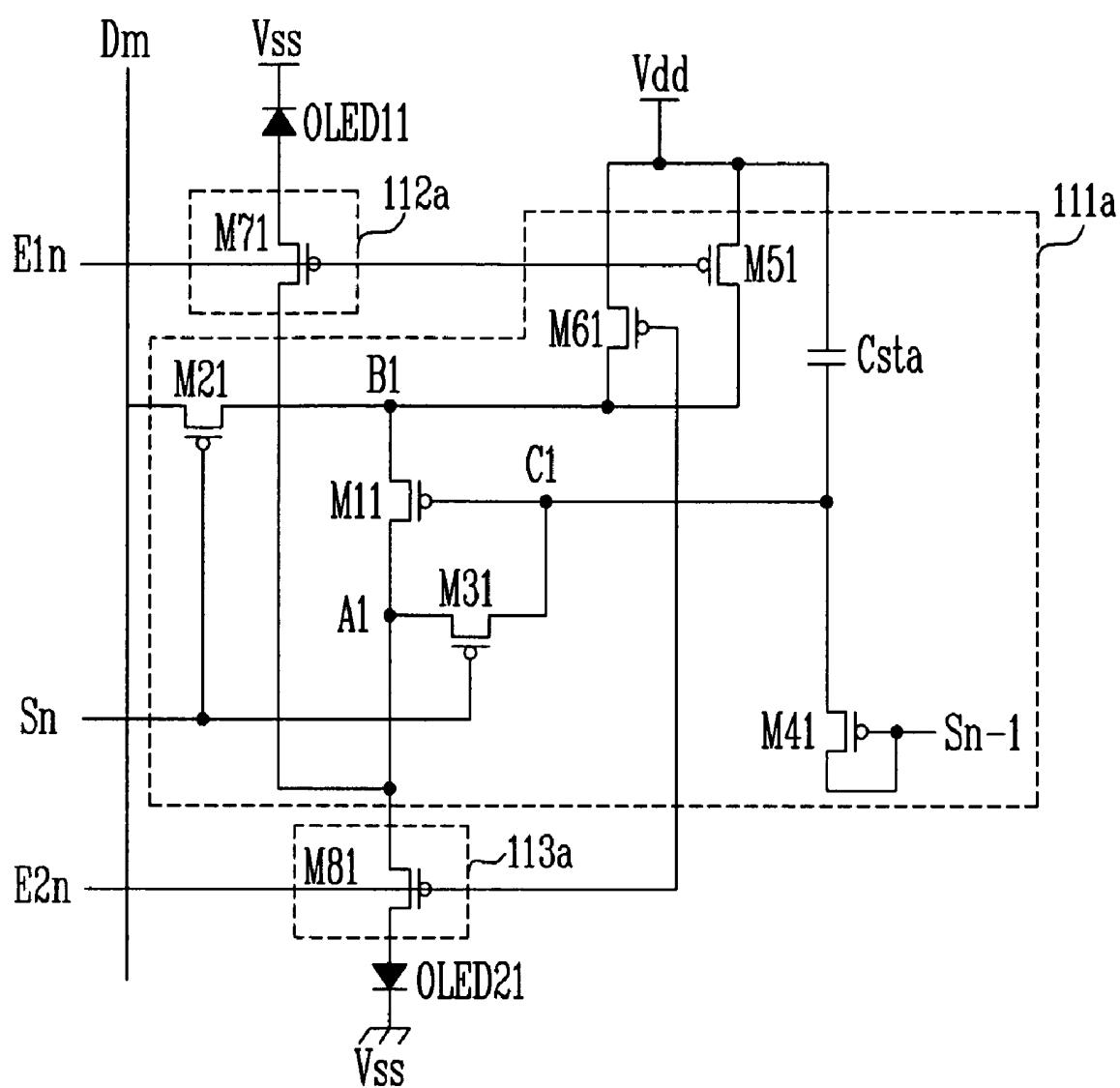

FIG. 3 is a circuit diagram illustrating a first embodiment of a pixel of the light emitting display of FIG. 2;

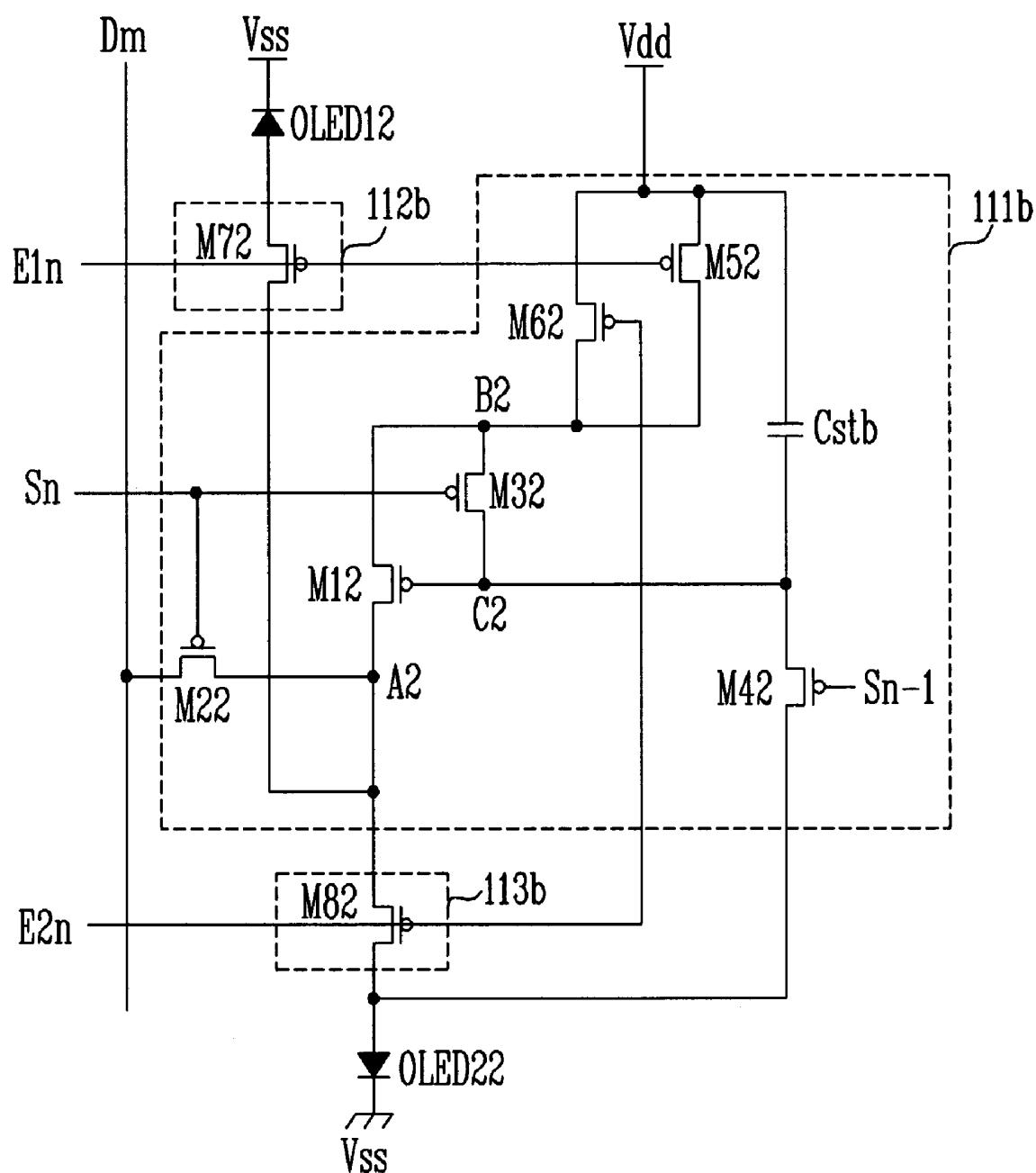

FIG. 4 is a circuit diagram illustrating a second embodiment of a pixel of the light emitting display of FIG. 2;

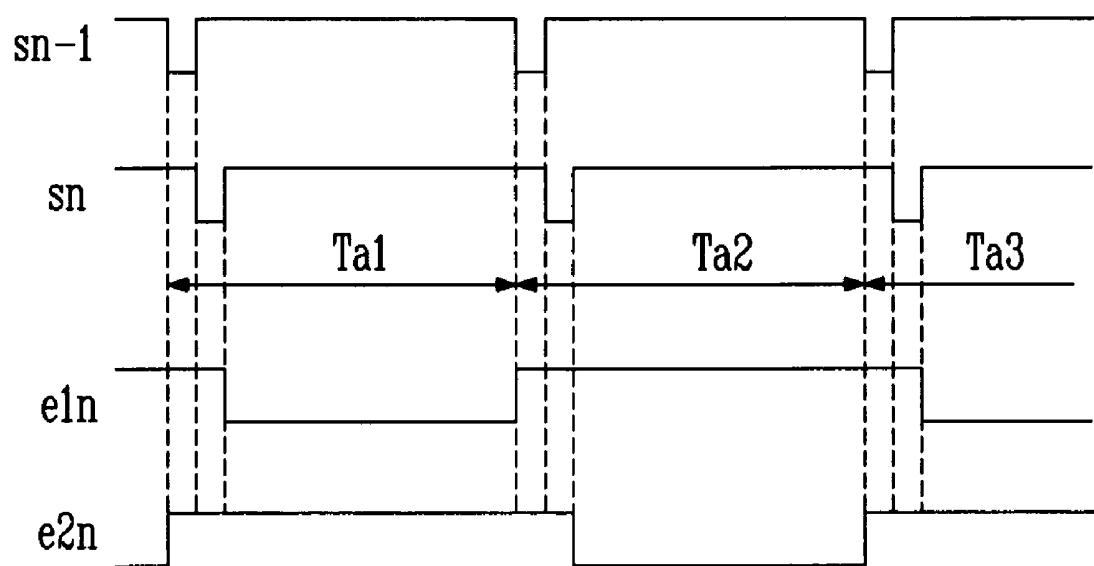

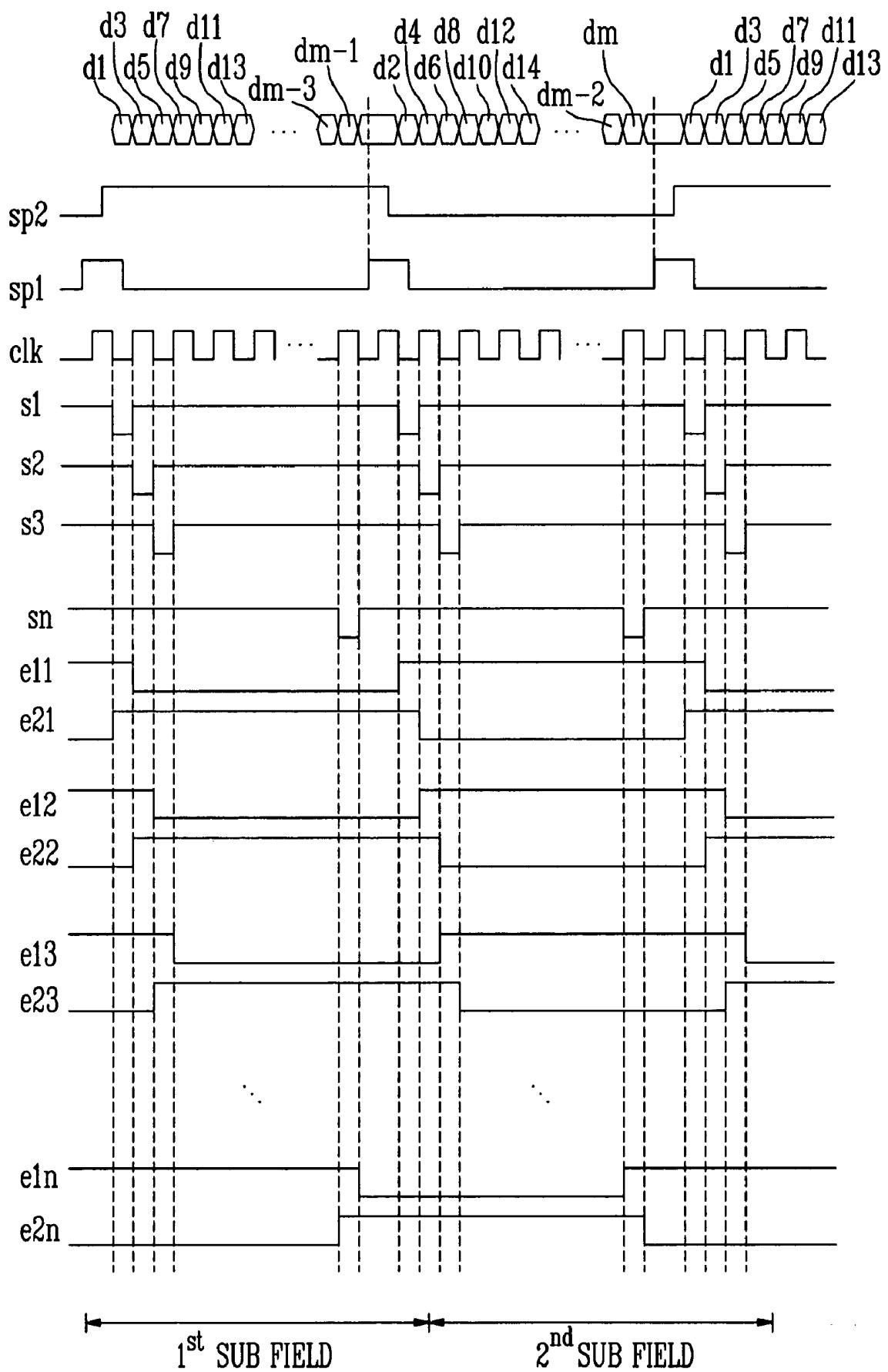

FIG. 5 is a timing diagram illustrating an operation of the pixels of FIGS. 3 and 4 according to an embodiment of the present invention;

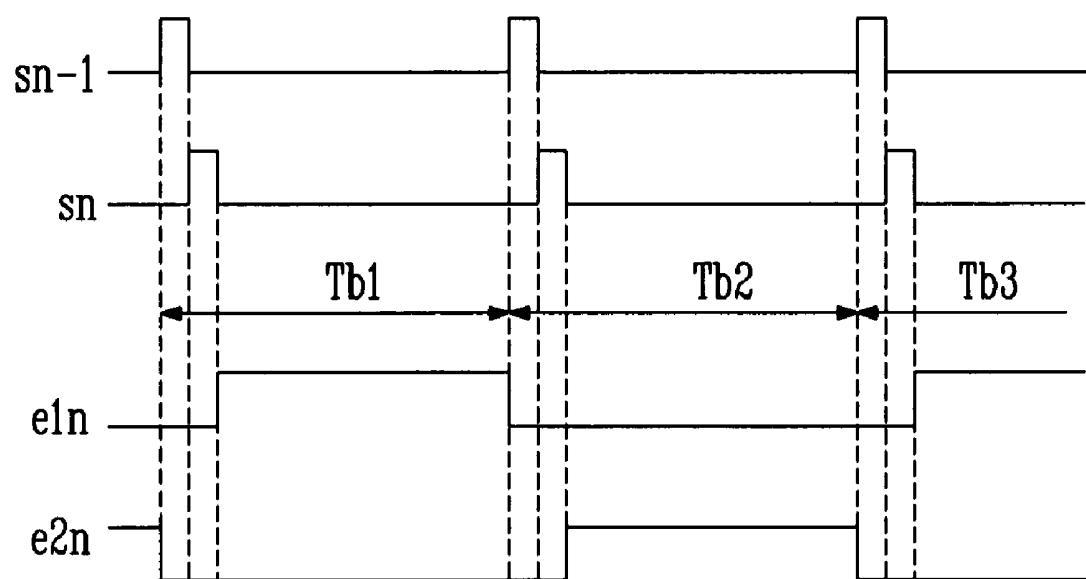

FIG. 6 is a timing diagram illustrating an operation of a case in which the pixels of FIGS. 3 and 4 are formed with NMOS transistors according to an embodiment of the present invention;

FIG. 7 is a timing diagram illustrating emission processes of a light emitting display according to an embodiment of the present invention;

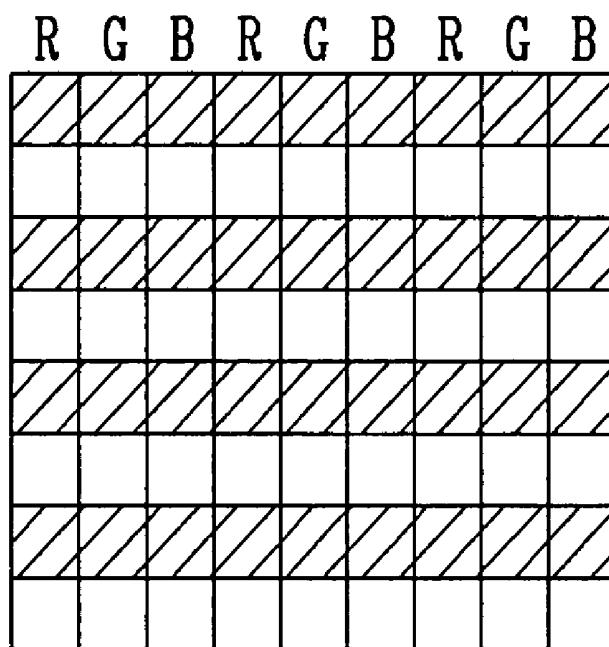

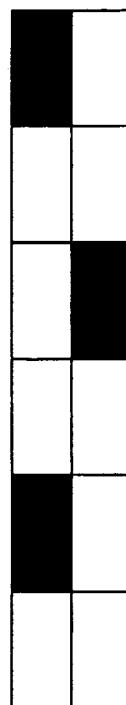

FIGS. 8A and 8B illustrate one frame of a light emitting display that is divided into two sub-fields;

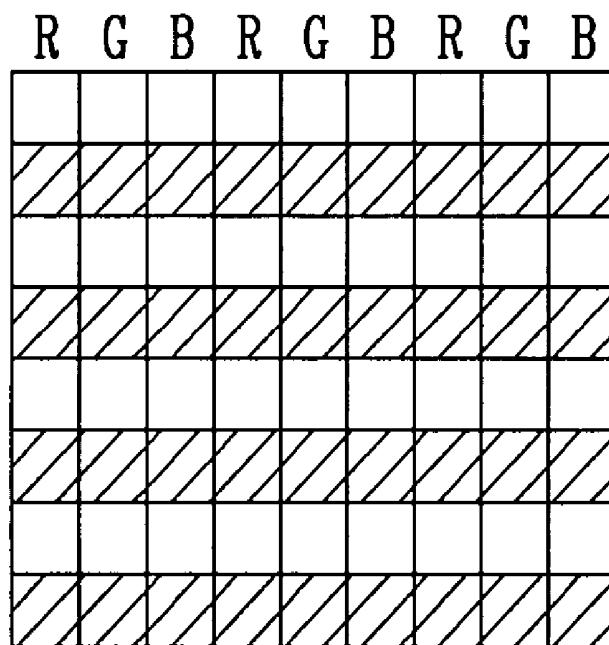

FIG. 9 illustrates a structure of a light emitting display of a second embodiment of the present invention;

FIG. 10 illustrates a structure of a light emitting display of a third embodiment of the present invention;

FIG. 11 is a circuit diagram illustrating an embodiment of a pixel of the light emitting display of FIG. 9;

FIG. 12 illustrates waveforms of signals transmitted to the light emitting display that uses the pixel of FIG. 11;

FIG. 13 is a circuit diagram illustrating a first embodiment of a pixel of the light emitting display of FIG. 10;

FIG. 14 is a circuit diagram illustrating a second embodiment of a pixel of the light emitting display of FIG. 10;

FIG. 15 illustrates waveforms of signals transmitted to the light emitting display that uses the pixels of FIGS. 13 and 14; and

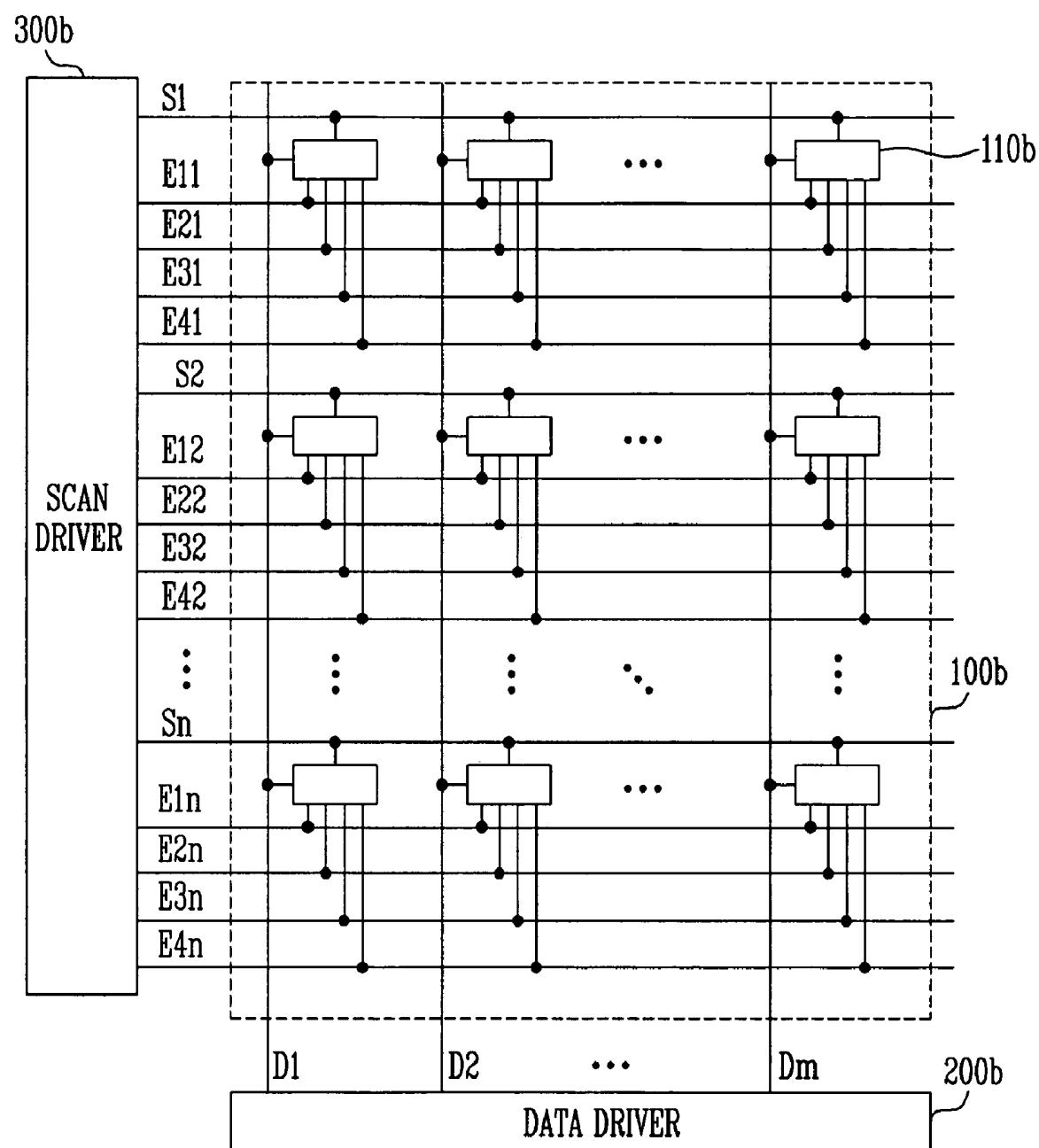

FIGS. 16A 16B, 16C and 16D illustrate emission processes of the light emitting display of FIG. 9.

#### DETAILED DESCRIPTION

In the following detailed description, certain exemplary embodiments of the present invention are shown and

described, by way of illustration. As those skilled in the art would recognize, the described exemplary embodiments may be modified in various ways, all without departing from the spirit or scope of the present invention. Accordingly, the drawings and description are to be regarded as illustrative in nature, rather than restrictive.

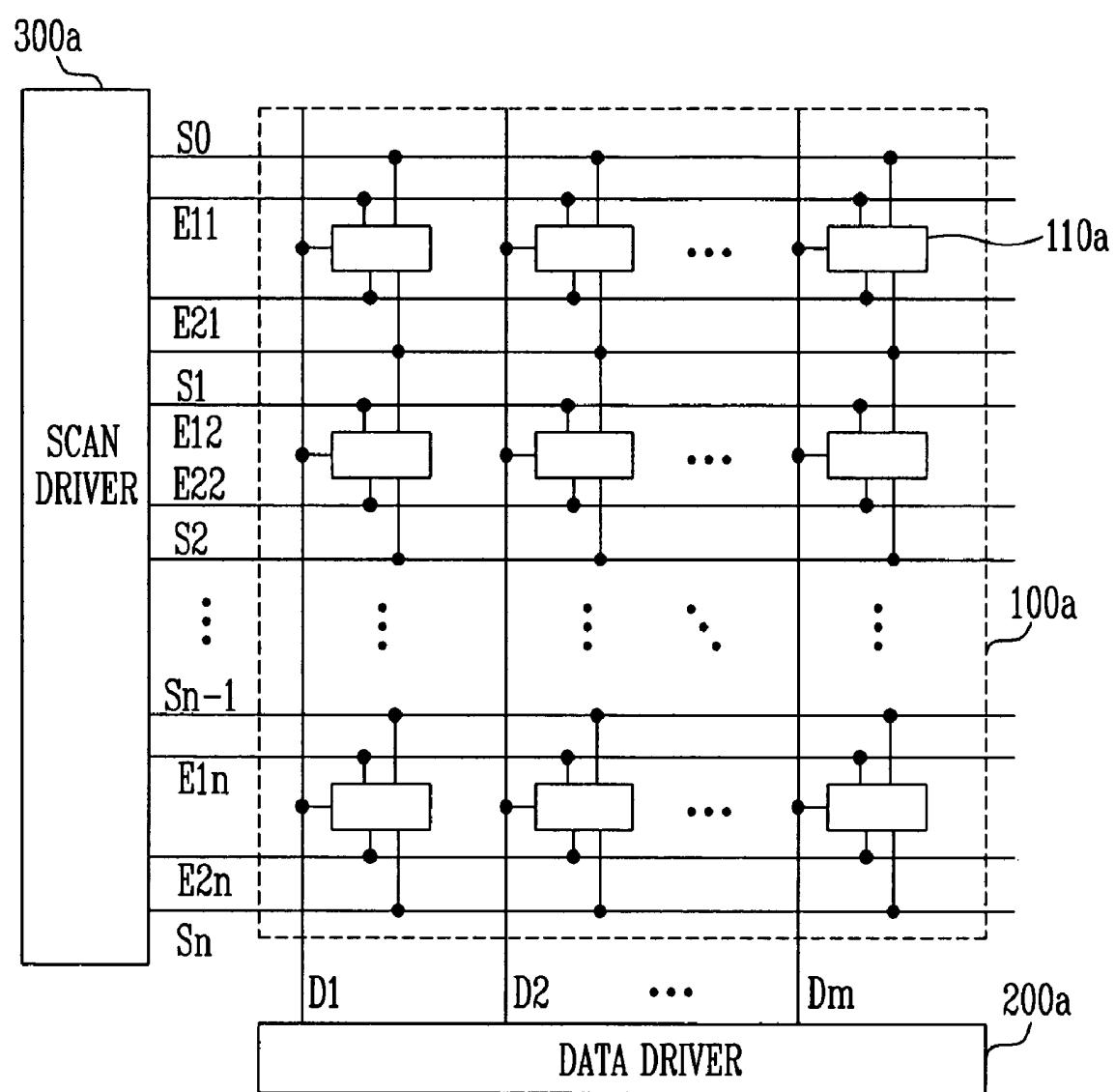

FIG. 2 illustrates a structure of a light emitting display of a first embodiment of the present invention. Referring to FIG. 2, the light emitting display includes an image display unit 100a, a data driver 200a, and a scan driver 300a.

The image display unit 100a includes a plurality of scan lines S0, S1, S2, ..., Sn-1, and Sn arranged in a row direction, a plurality of first emission control lines E11, E12, ..., E1n-1, and E1n and a plurality of second emission control lines E21, E22, ..., E2n-1, and E2n arranged in the row direction, a plurality of data lines D1, D2, ..., Dm-1, and Dm arranged in a column direction, a plurality of pixel power source lines (not shown) for supplying pixel power from a pixel power source, and a plurality of pixel circuits 110a. In the present embodiment, first and second OLEDs (not shown) are connected with each pixel circuit 110a.

Scan signals, data signals, and the pixel power transmitted from the scan lines S0, S1, S2, ..., Sn-1, and Sn, the data lines D1, D2, ..., Dm-1, and Dm, and the pixel power source lines are transmitted to the pixel circuits 110a so that second transistors (not shown) included in the pixel circuits 110a generate driving currents corresponding to the data signals. The driving currents are transmitted to the OLEDs in accordance with first and second emission control signals transmitted by the first emission control lines E11, E12, ..., E1n-1, and E1n and the second emission control lines E21, E22, ..., E2n-1, and E2n so that an image is displayed.

The first and second OLEDs are connected with one pixel circuit 110a and are positioned on a same column but on different rows. The first and second OLEDs emit the same color.

Therefore, since a current is supplied to two OLEDs, i.e., the first and second OLEDs through one pixel circuit 110a, the number of pixel circuits 110a can be reduced and thus improve an aperture ratio of the image display unit 100a. Since the first and second OLEDs emit the same color and are positioned on the same column, the same color data signal is input through one data line, and gamma correction can be more easily performed.

The data driver 200a is connected with the data lines D1, D2, ..., Dm-1, and Dm to transmit data signals to the image display unit 100a.

The scan driver 300a is formed on a side of the image display unit 100a and is connected with the scan lines S0, S1, S2, ..., Sn-1, and Sn, the first emission control lines E11, E12, ..., E1n-1, and E1n, and the second emission control lines E21, E22, E2n-1, and E2n to apply the scan signals and the first and second emission control signals to the image display unit 100a, thus sequentially selecting the rows of the image display unit 100a. Then, the data signals are applied to the selected rows by the data driver 200a so that the pixel circuit 110a emits light in accordance with the data signals and the first and second emission control signals.

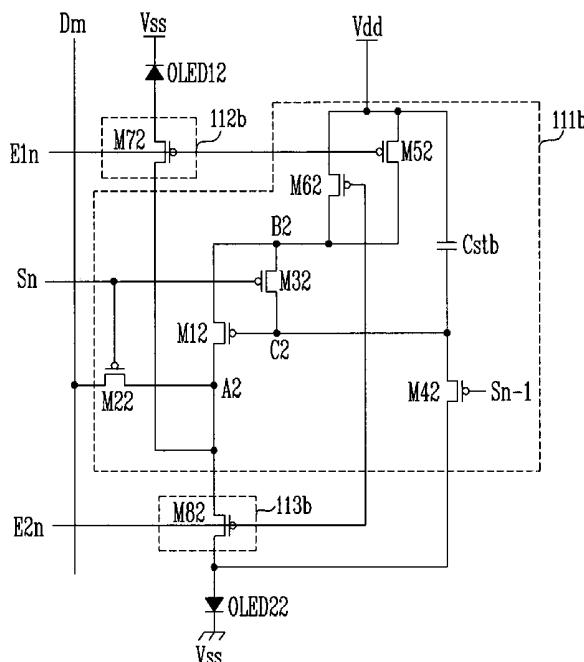

FIG. 3 is a circuit diagram illustrating a first embodiment of a pixel of the light emitting display of FIG. 2 according to the present invention. Referring to FIG. 3, the pixel includes a pixel circuit (e.g., the pixel circuit 110a) and OLEDs.

The pixel circuit includes a driving circuit 111a, a first switching circuit 112a, and a second switching circuit 113a. The driving circuit 111a includes first, second, third, fourth, fifth, and sixth transistors M11, M21, M31, M41, M51, and M61 and a capacitor Csta. The first switching circuit 112a

includes a seventh transistor M71. The second switching circuit 113a includes an eighth transistor M81. Each transistor includes a source, a drain, and a gate. The capacitor Csta includes a first electrode and a second electrode.

Since the drains and the sources of the first to eighth transistors M11 to M81 have no physical difference, each source and drain may be referred to as a first electrode and a second electrode.

The source of the first transistor M11 is connected with a first node A1, the drain of the first transistor M11 is connected with a second node B1, and the gate of the first transistor M11 is connected with a third node C1 so that a current flows from the first node A1 to the second node B1 in accordance with a voltage of the third node C1.

The source of the second transistor M21 is connected with a data line Dm, the drain of the second transistor M21 is connected with the second node B1, and the gate of the second transistor M21 is connected with a first scan line Sn so that the second transistor M21 performs a switching operation in accordance with a first scan signal sn transmitted through the first scan line Sn to selectively apply a data signal transmitted through the data line Dm to the second node B1.

The source of the third transistor M31 is connected with the third node C1, the drain of the third transistor M31 is connected with the first node A1, and the gate of the third transistor M31 is connected with the first scan line Sn so that the potential of the first node A1 is made equal to the potential of the third node C1 by the first scan signal sn transmitted through the first scan line Sn. Therefore, the first transistor M11 can be connected like a diode for an electric current to flow through the first transistor M11 (in one direction).

The source and gate of the fourth transistor M41 are connected with a second scan line Sn-1, and the drain of the fourth transistor M41 is connected with the third node C1 so that the fourth transistor M41 transmits an initializing signal to the third node C1. The initial signal is a second scan signal sn-1 input to select the row that precedes by one row the row to which the first scan signal sn is input to select. That is, the second scan line Sn-1 refers to the scan line connected with the row that precedes the row to which the first scan line Sn is connected by one row.

The source of the fifth transistor M51 is connected with a pixel power source Vdd, the drain of the fifth transistor M51 is connected with the second node B1, and the gate of the fifth transistor M51 is connected with a first emission control line E1n so that the fifth transistor M51 selectively applies a pixel power of the pixel power source Vdd to the second node B1 in accordance with a first emission control signal e1n transmitted through the first emission control line E1n.

The source of the seventh transistor M71 is connected with the first node A1, the drain of the seventh transistor M71 is connected with a first OLED OLED11, and the gate of the seventh transistor M71 is connected with the first emission control line E1n so that the seventh transistor M71 applies a current input through the first node A1 to the first OLED OLED11 in accordance with the first emission control signal e1n transmitted through the first emission control line E1n.

The source of the sixth transistor M61 is connected with the pixel power source Vdd, the drain of the sixth transistor M61 is connected with the second node B1, and the gate of the sixth transistor M61 is connected with a second emission control signal E2n so that the sixth transistor M61 selectively applies the pixel power of the pixel power source Vdd to the second node B1 in accordance with a second emission control signal e2n transmitted through the second emission control signal E2n.

The source of the eighth transistor M81 is connected with the first node A1, the drain of the eighth transistor M81 is connected with a second OLED OLED21, and the gate of the eighth transistor M81 is connected with the second emission control line E2n so that the eighth transistor M81 applies a current input through the first node A1 to the second OLED OLED21 in accordance with the second emission control signal e2n transmitted through the second emission control line E2n.

The first electrode of the capacitor Csta is connected with the pixel power source Vdd, and the second electrode of the capacitor Csta is connected with the third node C1 so that the capacitor Csta is initialized by the initializing signal transmitted through the fourth transistor M41. The capacitor Csta maintains the voltage applied to the gate of the first transistor M11 for a predetermined time.

The OLEDs of the pixel of FIG. 3 include the first OLED OLED11 and the second OLED OLED21. The first OLED OLED11 and the second OLED OLED21 are connected with the seventh transistor M71 and the eighth transistor M81, respectively, to receive a current. The input of the current is controlled by the first emission control line E1n and the second emission control line E2n. The first OLED OLED11 and the second OLED OLED21 are positioned on the same column but on different rows.

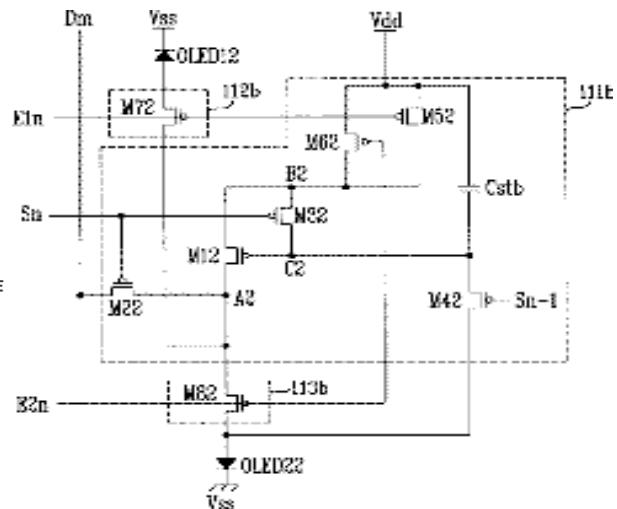

FIG. 4 is a circuit diagram illustrating a second embodiment of a pixel of the light emitting display of FIG. 2. Referring to FIG. 4, the pixel includes a pixel circuit and OLEDs.

The pixel circuit includes a driving circuit 111b, a first switching circuit 112b, and a second switching circuit 113b. The driving circuit 111b includes first, second, third, fourth, fifth, and sixth transistors M12, M22, M32, M42, M52, and M62 and a capacitor Cstb. The first switching circuit 112b includes a seventh transistor M72. The second switching circuit 113b includes an eighth transistor M82. Each transistor includes a source, a drain, and a gate. The capacitor Cstb includes a first electrode and a second electrode.

Since the drains and the sources of the first to eighth transistors M12 to M82 have no physical difference, each source and drain may be referred to as a first electrode and a second electrode.

The drain of the first transistor M12 is connected with a first node A2, the source of the first transistor M12 is connected with a second node B2, and the gate of the first transistor M12 is connected with a third node C2 so that a current flows from the first node A2 to the second node B2 in accordance with a voltage of the third node C2.

The source of the second transistor M22 is connected with a data line Dm, the drain of the second transistor M22 is connected with the first node A2, and the gate of the second transistor M22 is connected with a first scan line Sn so that the second transistor M22 performs a switching operation in accordance with a first scan signal sn transmitted through the first scan line Sn to selectively apply a data signal transmitted through the data line Dm to the first node A2.

The source of the third transistor M32 is connected with the second node B2, the drain of the third transistor M32 is connected with the third node C2, and the gate of the third transistor M32 is connected with the first scan line Sn so that the potential of the second node B2 is made equal to the potential of the third node C2 by the first scan signal sn transmitted through the first scan line Sn. Therefore, the first transistor M12 can serve as a diode for an electric current to flow through the first transistor M12 (in one direction).

The source of the fourth transistor M42 is connected with an anode electrode of an OLED22, the gate of the fourth transistor M42 is connected with a second scan line Sn-1, and

the drain of the fourth transistor M42 is connected with the third node C2. The fourth transistor M42 applies a voltage between the OLED22 and a cathode electrode Vss when no current flows through the OLED22 to the third node C2 in accordance with a second scan signal sn-1 transmitted by the second scan line Sn-1 and uses the voltage between the OLED22 and the cathode voltage Vss as an initializing signal.

The source of the fifth transistor M52 is connected with a pixel power source Vdd, the drain of the fifth transistor M52 is connected with the second node B2, and the gate of the fifth transistor M52 is connected with a first emission control line E1n so that the fifth transistor M52 selectively applies a pixel power of the pixel power source Vdd to the second node B2 in accordance with a first emission control signal e1n transmitted through the first emission control line E1n.

The source of the sixth transistor M62 is connected with the pixel power source Vdd, the drain of the sixth transistor M62 is connected with the second node B2, and the gate of the sixth transistor M62 is connected with a second emission control signal E2n so that the sixth transistor M62 selectively applies the pixel power of the pixel power source Vdd to the second node B2 in accordance with a second emission control signal e2n transmitted through the second emission control signal E2n.

The source of the seventh transistor M72 is connected with the first node A2, the drain of the seventh transistor M72 is connected with a first OLED OLED12, and the gate of the seventh transistor M72 is connected with the first emission control line E1n so that the seventh transistor M72 applies a current input through the first node A2 to the first OLED OLED12 in accordance with the first emission control signal e1n transmitted through the first emission control line E1n.

The source of the eighth transistor M82 is connected with the first node A2, the drain of the eighth transistor M82 is connected with a second OLED OLED22, and the gate of the eighth transistor M82 is connected with the second emission control line E2n so that the eighth transistor M82 applies a current input through the first node A2 to the second OLED OLED22 in accordance with the second emission control signal e2n transmitted through the second emission control line E2n.

The first electrode of the capacitor Cstb is connected with the pixel power source Vdd and the second electrode of the capacitor Cstb is connected with the third node C2 so that the capacitor Cstb is initialized by the initializing signal transmitted through the fourth transistor M42. The capacitor Cstb maintains the gate voltage of the first transistor M12 for a predetermined time.

The OLEDs of the pixel of FIG. 4 include the first OLED OLED12 and the second OLED OLED22. The first OLED OLED12 and the second OLED OLED22 are connected with the seventh transistor M71 and the eighth transistor M82, respectively, to receive a current. The input of the current is controlled by the first emission control line E1n and the second emission control line E2n. The first OLED OLED12 and the second OLED OLED22 are positioned on the same column but on different rows.

FIG. 5 is a timing diagram illustrating an operation of the pixels of FIGS. 3 and 4. Referring to FIG. 5, each of the pixels is operated by a first scan signal sn, a second scan signal sn-1, a first emission control signal e1n, and a second emission control signal e2n. The operation of the pixel is divided into a first period T11 in which a first OLED OLED1 (e.g., OLED11 or OLED12) emits light and a second period Ta2 in which a second OLED OLED2 (e.g., OLED21 or OLED22) emits light.

In the first period Ta1, the second scan signal sn-1 is first transited from a high level to a low level while the first scan signal sn, the first emission control signal e1n, and the second emission control signal e2n are each maintained at the high level so that a fourth transistor M4 (e.g., M41 or M42) is turned on. Therefore, the initializing signal is transmitted to a third node C (e.g., C1 or C2) to initialize a capacitor Cst (e.g., Csta or Cstb). At this time, in FIG. 3, the initializing signal is formed by the second scan signal sn-1. In FIG. 4, the initializing signal is formed by the voltage applied to the OLEDs (e.g., OLED22) when seventh and eighth transistors MT (e.g., M72) and M8 (e.g., M82) are turned off by the first and second emission control signals e1n and e2n.

Then, after the second scan signal sn-1 is transited from the low level to the high level in the first period Ta1, the first scan signal sn is transited from the high level to the low level while the first and second emission control signals e1n and e2n are each maintained at the high level so that second and third transistors M2 (e.g., M21 or M22) and M3 (e.g., M31 or M32) are turned on. When the second and third transistors M2 and M3 are turned on, the potential of a first node A (e.g., A1) or a second node B (e.g., B2) is equal to the potential of a third node C (e.g., C1 or C2) so that an electric current flows through a first transistor M1 (e.g., M11 or M12) serving as a diode; so that the data signal transmitted through a data line is applied to the third node C through the first transistor M1 serving as the diode through which the electric current flows; and so that a voltage corresponding to a difference between the voltage of the data signal and the threshold voltage of the first transistor M is applied to a second electrode of the capacitor Cst.

After the first scan signal sn is transited to the high level and maintained at the high level for a predetermined time, when the first emission control signal e1n is transited to the low level and maintained at the low level for a predetermined time, the first scan signal sn, the second scan signal sn-1, and the second emission control signal e2n are each maintained at the high level while the first emission control signal e1n is in the low level. At this time, fifth and seventh transistors M5 (e.g., M51 or M52) and M7 (e.g., M71 or M72) are turned on by the first emission control signal e1n so that the voltage obtained by EQUATION 1 is applied between the gate and source of the first transistor M1.

$$V_{sg} = Vdd - (V_{data} - |V_{th}|) \quad [EQUATION 1]$$

wherein, Vsg, Vdd, Vdata, and Vth represent the voltage between the source and the gate of the first transistor M1, a pixel power source voltage, the voltage of the data signal, and the threshold voltage of the first transistor M1, respectively.

The seventh transistor M7 is turned on so that the current obtained by EQUATION 2 flows to the OLED OLED1.

$$\begin{aligned} I_{OLED} &= \frac{\beta}{2} (V_{gs} - |V_{th}|)^2 \\ &= \frac{\beta}{2} (V_{data} - Vdd + |V_{th}| - |V_{th}|)^2 \\ &= \frac{\beta}{2} (V_{data} - Vdd) \end{aligned} \quad [EQUATION 2]$$

wherein,  $I_{OLED}$ , Vgs, Vdd, Vth, and Vdata represent the current that flows to the OLED OLED1, the voltage applied to the gate of the first transistor M1, the voltage of the pixel power source, the threshold voltage of the first transistor M1, and the voltage of the data signal, respectively.

Therefore, as shown by EQUATION 2, the current flows to the first OLED OLED1 regardless of the threshold voltage of the first transistor M1.

In the second period Ta2, after the second scan signal sn-1 is again in the low level to initialize the capacitor Cst, the first scan signal sn is in the low level to transmit the data signal to the first node A (e.g., A1 or A2). An electric current flows through the first transistor M1 serving as a diode due to the third transistor M3 so that the voltage corresponding to the voltage of the data signal is stored in the capacitor Cst and that the voltage obtained by the EQUATION 1 is applied between the source and gate of the first transistor M1.

Then, when the second emission control signal e2n maintains the low level for a predetermined time, sixth and eighth transistors M6 (e.g., M61 or M62) and M8 (e.g., M81 or M82) are turned on so that the current obtained by the EQUATION 2 flows to the second OLED OLED2.

Therefore, the first and second OLEDs OLED1 and OLED2 connected with one pixel circuit sequentially emit light.

FIG. 6 is a timing diagram illustrating an operation of a case in which the pixels of FIGS. 3 and 4 are formed with NMOS transistors instead of PMOS transistors. Referring to FIG. 6, each of the pixels is operated by a first scan signal sn, a second scan signal sn-1, a first emission control signal e1n, and a second emission control signal e2n. The operation of the pixel is divided into a first period Tb1 in which a first OLED (e.g., OLED11 or OLED12) emits light and a second period Tb2 in which a second OLED (e.g., OLED21 or OLED22) emits light.

FIG. 7 is a timing diagram illustrating emission processes of a light emitting display according to an embodiment of the present invention. Referring to FIG. 7, serially input data signals are divided into first data signals d1, d3, ..., dm-3, and dm-1 input to odd rows and second data signals d2, d4, ..., dm-2, and dm input to even rows. When the first data signals d1, d3, ..., dm-3, and dm-1 are output from a data driver (e.g., the data driver 200a) and input to the odd rows, the second data signals d2, d4, ..., dm-2, and dm are input to the data driver (e.g., the data driver 200a). Here, the numbers between 1 and refer to the row numbers of the light emitting display. A period in which the odd rows emit light is referred to as a first sub-field, and a period in which the even rows emit light is referred to as a second sub-field. One frame is composed of the first sub-field and the second sub-field.

In operation, the first data signals d1, d3, ..., dm-3, and dm-1 are first sequentially input to the odd rows in accordance with scan signals (e.g., s1, s2, s3, ... and sn). At this time, first emission control signals (e.g., e11, e12, e13, ..., e1n) are sequentially input so that a first OLED (e.g., OLED 11 or OLED 12) in each pixel circuit emits light and so that the odd rows emit light as a result. Therefore, referring to FIG. 8A, the first sub-field emits light as illustrated in FIG. 8A.

Then, the second data signals d2, d4, ..., dm-2, and dm are sequentially input to the even rows in accordance with the scan signals. At this time, second emission control signals are sequentially input to the even rows so that a second OLED (e.g., OLED 21 or OLED 22) in each pixel circuit emits light and so that the even rows emit light as a result. Therefore, referring to FIG. 8B, the second sub-field emits light as illustrated in FIG. 8B.

When the first and second sub-fields emit light, all of the OLEDs emit light to complete one frame.

FIG. 9 illustrates a structure of a light emitting display of a second embodiment of the present invention. Referring to FIG. 9, the light emitting display includes an image display unit 100b, a data driver 200b, and a scan driver 300b.

The image display unit 100b includes a plurality of pixel circuits 110b, a plurality of scan lines S1, S2, ..., Sn-1, and Sn arranged in a row direction, a plurality of first emission control lines E11, E12, ..., E1n-1, and E1n, second emission control lines E21, E22, ..., E2n-1, and E2n, third emission control lines E31, E32, ..., and E3n-1, and E3n, and fourth emission control lines E41, E42, ..., E4n-1, and E4n arranged in the row direction, a plurality of data lines D1, D2, ..., Dm-1, and Dm arranged in a column direction, and a plurality of pixel power source lines (not shown) for supplying pixel power. The pixel power source lines receive the pixel power from an outside pixel power source that supplies the pixel power.

The data signals transmitted from the data lines D1, D2, ..., Dm-1, and Dm are transmitted to the pixel circuit 110b in accordance with scan signals transmitted from the scan lines S1, S2, ..., Sn-1, and Sn and scan signals. The pixel circuits 110b generate currents corresponding to the data signals, and the currents are transmitted to the OLEDs in accordance with first, second, third and fourth emission control signals transmitted through the first emission control lines E11, E12, ..., E1n-1, and E1n to the fourth emission control lines E41, E42, ..., E4n-1, and E4n so that an image is displayed.

The data driver 200b is connected with the data lines D1, D2, ..., Dm-1, and Dm to transmit the data signals to the image display unit 100b. The data driver 200b sequentially transmits red and green, green and blue, or blue and red data to one data line.

The scan driver 300b is formed on a side of the image display unit 100b and is connected with the plurality of scan lines S1, S2, ..., Sn-1, and Sn and the plurality of first emission control lines E11, E12, ..., E1n-1, and E1n to the fourth emission control lines E41, E42, ..., E4n-1, and E4n so that the scan signals and the first, second, third and fourth emission control signals are transmitted to the image display unit 100b.

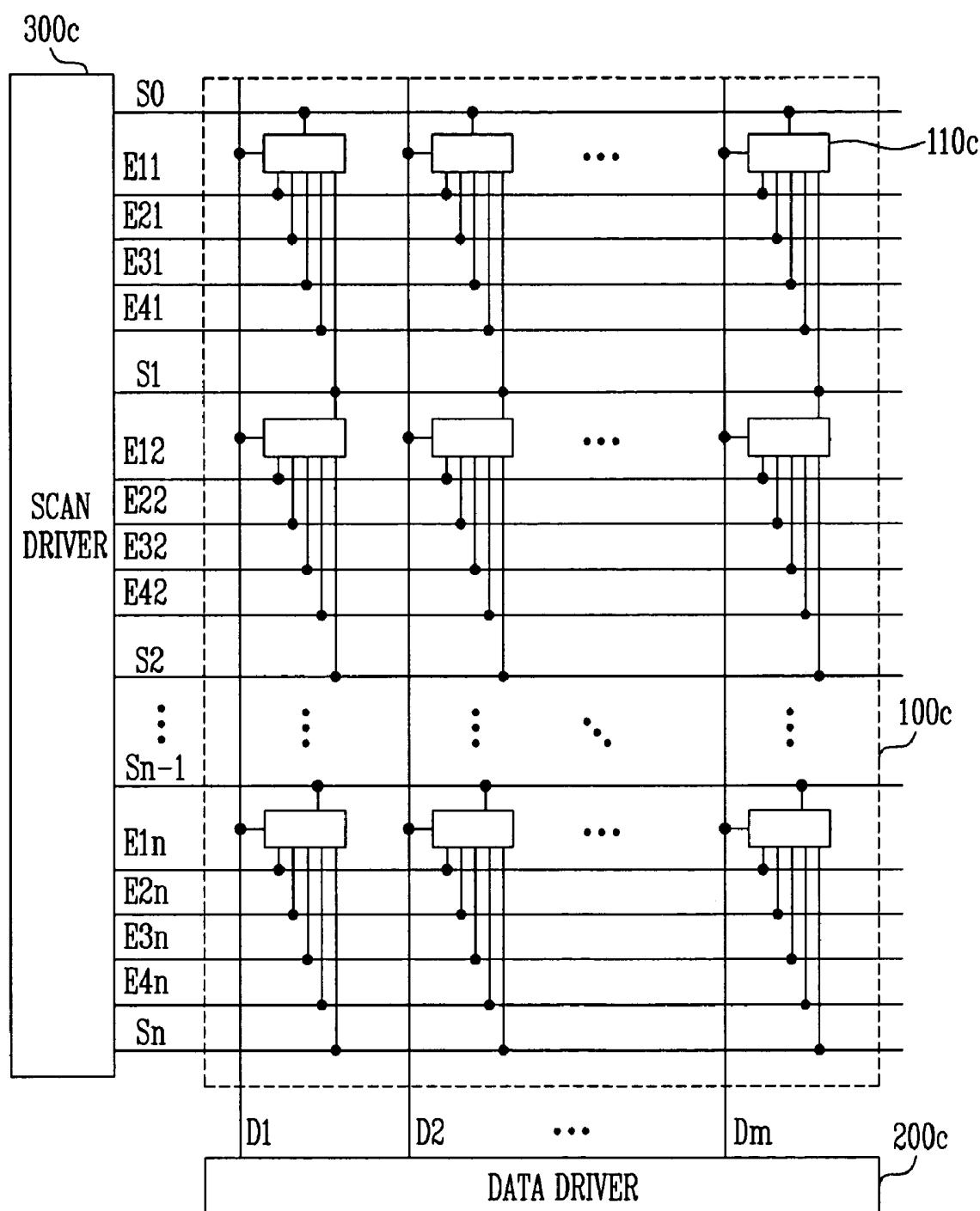

FIG. 10 illustrates a structure of a light emitting display according to a third embodiment of the present invention. Referring to FIG. 10, the light emitting display includes an image display unit 100c, a data driver 200c, and a scan driver 300c.

The image display unit 100c includes a plurality of pixel circuits 110c, four OLEDs (not shown) connected with each of the pixel circuits 110c, a plurality of scan lines S0, S1, S2, ..., Sn-1, and Sn arranged in a row direction, a plurality of first emission control lines E11, E12, ..., E1n-1, and E1n, second emission control lines E21, E22, ..., E2n-1, and E2n, third emission control lines E31, E32, ..., and E3n-1, and E3n, and fourth emission control lines E41, E42, ..., E4n-1, and E4n arranged in the row direction, a plurality of data lines D1, D2, ..., Dm-1, and Dm arranged in a column direction, and a plurality of pixel power source lines (not shown) for supplying pixel power. The pixel power source lines receive the pixel power from an outside pixel power source that supplies the pixel power.

Each of the pixel circuits 110c receives a scan signal of a current scan line and a scan signal of a previous scan line through the scan lines S0, S1, S2, ..., Sn-1, and Sn (e.g., Sn-1 and Sn) and generates currents corresponding to the data signals transmitted from the data lines D1, D2, ..., Dm-1, and Dm. The driving currents are transmitted to the four OLEDs in accordance with first, second, third and fourth emission control signals transmitted through the first emission control lines E11, E12, ..., E1n-1, and E1n to the fourth emission control lines E41, E42, ..., E4n-1, and E4n so that an image is displayed.

The data driver 200c is connected with the data lines D1, D2, ..., Dm-1, and Dm to transmit the data signals to the image display unit 100c. The data driver 200c sequentially transmits red and green, green and blue, or blue and red data to one data line.

The scan driver 300c is formed on a side of the image display unit 100c and is connected with the plurality of scan lines S0, S1, S2, ..., Sn-1, and Sn and the plurality of first emission control lines E11, E12, ..., E1n-1, and E1n to the fourth emission control lines E41, E42, ..., E4n-1, and E4n so that the scan signals and the first, second, third and fourth emission control signals are transmitted to the image display unit 100c.

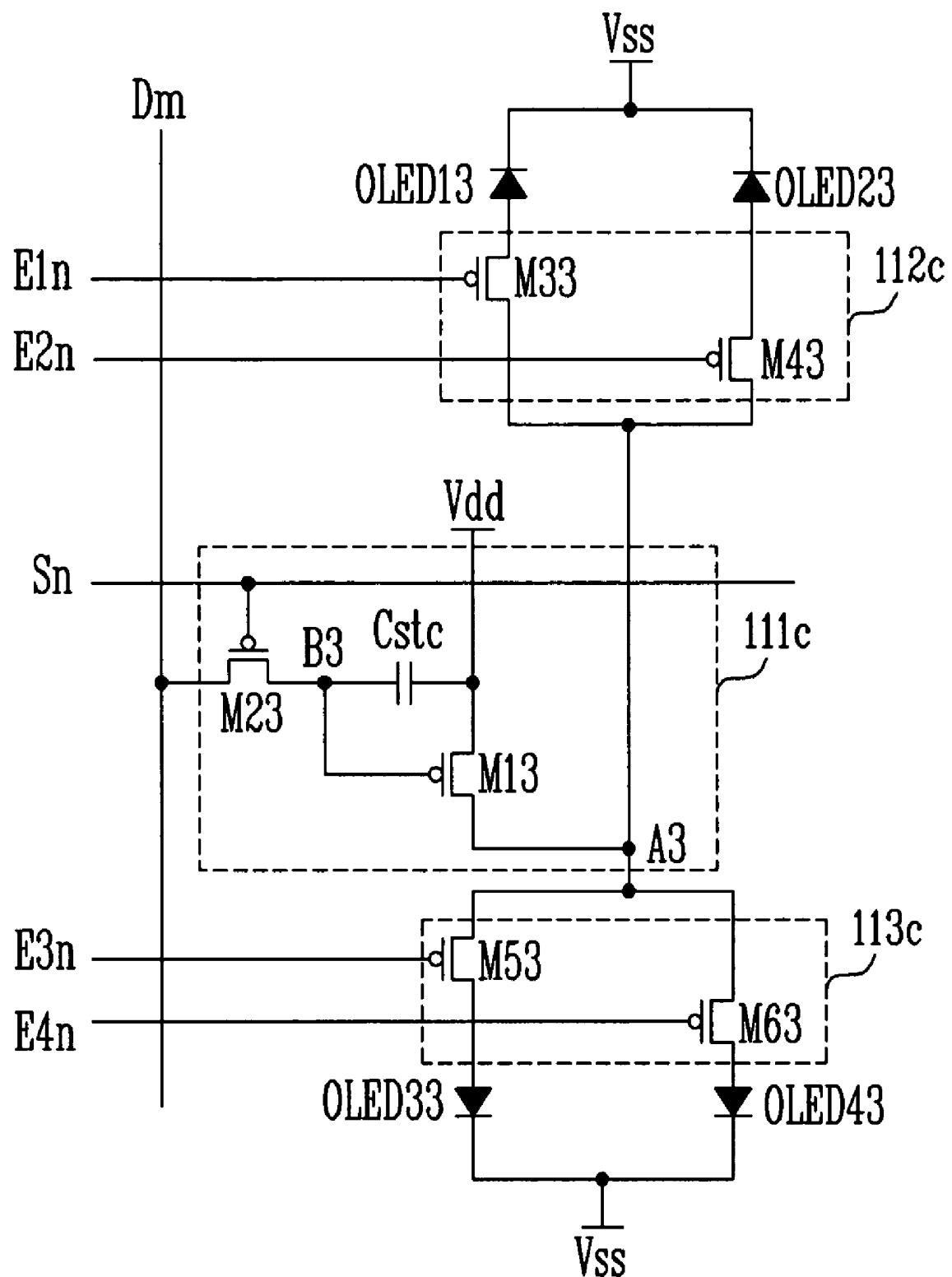

FIG. 11 is a circuit diagram illustrating an embodiment of a pixel of the light emitting display of FIG. 9. Referring to FIG. 11, the pixel includes four OLEDs and a pixel circuit (e.g., the pixel circuit 110b). The four OLEDs OLED13, OLED23, OLED33, and OLED43 are connected with one pixel circuit. The pixel circuit (e.g., the pixel circuit 110b) includes a driving circuit 111c, a first switching circuit 112c, and a second switching circuit 113c.

The driving circuit 111c includes first and second transistors M13 and M23 and a capacitor Cstc. The first switching circuit 112c includes third and fourth transistors M33 and M43. The second switching circuit 113c includes fifth and sixth transistors M53 and M63.

Each of the first to sixth transistors M13 to M63 includes a source, a drain, and a gate. Since the drains and the sources of the first to sixth transistors M13 to M63 have no physical difference, each source and drain may be referred to as a first electrode and a second electrode. Also, the capacitor Cstc includes a first electrode and a second electrode. The four OLEDs are referred to as first to fourth OLEDs OLED13 to OLED43.

The source of the first transistor M13 is connected with a pixel power source line Vdd, the drain of the first transistor M13 is connected with a first node A3, and the gate of the first transistor M13 is connected with a second node B3 so that an amount of current that flows from the source of the first transistor M13 to the drain of the first transistor M13 is determined in accordance with a voltage applied to the gate of the first transistor M13.

The source of the second transistor M23 is connected with a data line Dm, the drain of the second transistor M23 is connected with the second node B3, and the gate of the second transistor M23 is connected with a scan line Sn so that the second transistor M23 performs on and off operations in accordance with a scan signal sn transmitted through the scan line Sn to selectively apply a data signal to the second node B3.

The source of the third transistor M33 is connected with the first node A3, the drain of the third transistor M33 is connected with the first OLED OLED13, and the gate of the third transistor M33 is connected with a first emission control line E1n so that the third transistor M33 performs on and off operations in accordance with a first emission control signal e1n received through the first emission control line E1n to selectively apply the current that flows through the first node A3 to the first OLED OLED13.

The source of the fourth transistor M43 is connected with the first node A3, the drain of the fourth transistor M43 is connected with the second OLED OLED23, and the gate of the fourth transistor M43 is connected with a second emission control line E2n so that the fourth transistor M43 performs on and off operations in accordance with a second emission control signal e2n received through the second emission control line E2n.

trol line  $E2n$  to selectively apply the current that flows through the first node  $A3$  to the second OLED OLED23.

The source of the fifth transistor M53 is connected with the first node A3, the drain of the fifth transistor M53 is connected with the third OLED OLED33, and the gate of the fifth transistor M53 is connected with a third emission control line  $E3n$  so that the fifth transistor M53 selectively applies the current that flows from the source of the fifth transistor M53 to the drain of the fifth transistor M53, to the third OLED OLED33 in accordance with a third emission control signal  $e3n$  transmitted through the third emission control line  $E3n$  to emit light from the third OLED OLED33.

The source of the sixth transistor M63 is connected with the first node A3, the drain of the sixth transistor M63 is connected with the fourth OLED OLED43, and the gate of the sixth transistor M63 is connected with a fourth emission control line  $E4n$  so that the sixth transistor M63 selectively applies the current that flows from the source of the sixth transistor M63 to the drain of the sixth transistor M63, to the fourth OLED OLED43 in accordance with a fourth emission control signal  $e4n$  transmitted through the fourth emission control line  $E4n$  to emit light from the fourth OLED OLED43.

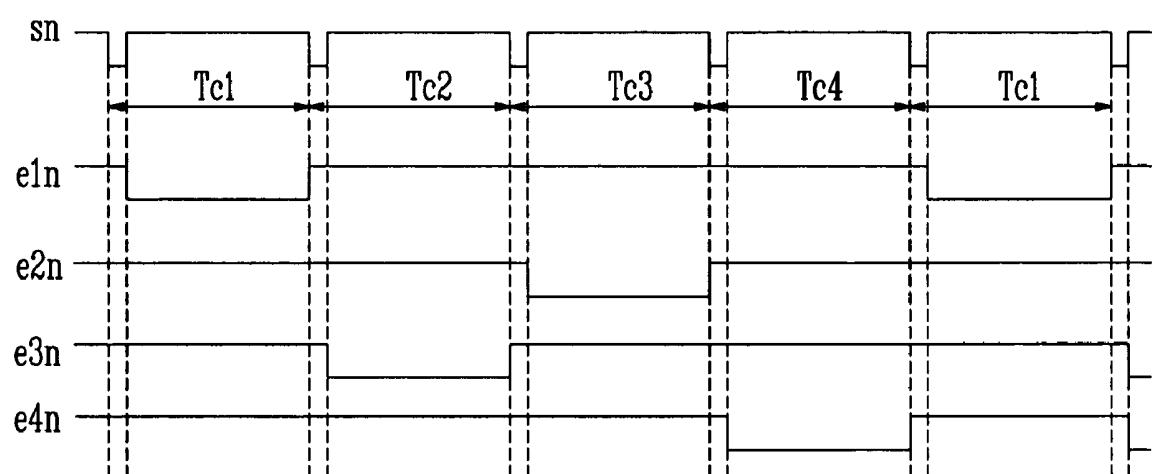

FIG. 12 illustrates waveforms of signals transmitted to the light emitting display that uses the pixel of FIG. 11. Referring to FIG. 12, the pixel is operated by a scan signal  $sn$ , a data signal, and first, second, third and fourth emission control signals  $e1n$  to  $e4n$ . The scan signal  $sn$  and the first to fourth emission control signals  $e1n$  to  $e4n$  are periodical signals having first to fourth periods T1 to T4.

In the first period Tc1, the first emission control signal  $e1n$  is in a low level. In the second period Tc2, the third emission control signal  $e3n$  is in the low level. In the third period Tc3, the second emission control signal  $e2n$  is in the low level. In the fourth period Tc4, the fourth emission control signal  $e4n$  is in the low level. The scan signal  $sn$  is in the low level for a moment at the start point of each period.

In the first period Tc1, a second transistor M23 is turned on by the scan signal  $sn$  so that the data signal is transmitted to a second node B3 through the second transistor M23. The pixel power is transmitted to the first electrode of a capacitor Cstc so that a voltage value corresponding to a difference  $Vdd - Vdata$  between the pixel power and the data signal is stored in the capacitor Cstc.

The capacitor Cstc applies the voltage corresponding to the difference between the pixel power and the data signal to the gate of a first transistor M13 through the second node B3 so that the first transistor M13 flows a current corresponding to the data signal to a first node A3.

A third transistor M33 is turned on by the first emission control signal  $e1n$  so that the current flows to the first OLED OLED13.

In the second period Tc2, the voltage value corresponding to the difference between the pixel power source and the data signal is stored in the capacitor Cstc by the scan signal  $sn$  and the data signal so that the first transistor M13 flows the current corresponding to the data signal to the first node A3. The fifth transistor M53 is turned on by the third emission control signal  $e3n$  so that the current flows to the third OLED OLED33.

In the third and fourth periods Tc3 and Tc4, a current is generated as in the first and second periods Tc1 and Tc2, and the current flows to the first node A3. In the third period Tc3, the current flows to the second OLED OLED23 by the second emission control signal  $e2n$ . In the fourth period Tc4, the current flows to the fourth OLED OLED43 by the fourth emission control signal  $e4n$ .

Therefore, the first to fourth OLEDs OLED13 to OLED43 sequentially emit light in the order described above.

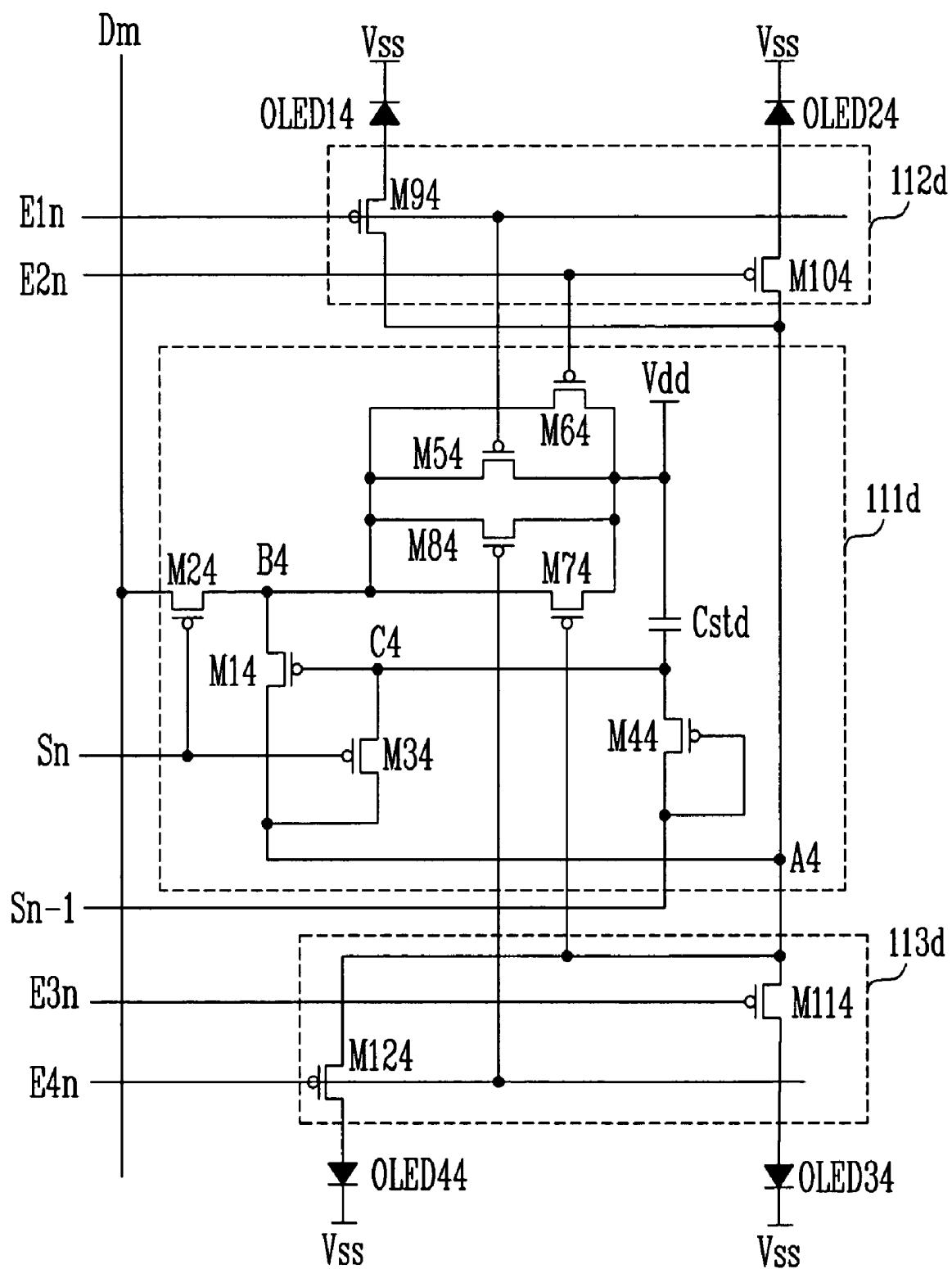

FIG. 13 is a circuit diagram illustrating a first embodiment of a pixel of the light emitting display of FIG. 10. Referring to FIG. 13, the pixel includes four OLEDs and a pixel circuit (e.g., the pixel circuit 110c). The four OLEDs OLED14, OLED24, OLED34, and OLED44 are connected with one pixel circuit. The pixel circuit (e.g., the pixel circuit 110c) includes a driving circuit 111d, a first switching circuit 112d, and a second switching circuit 113d.

The driving circuit 111d includes first to eighth transistors M14 to M84 and a capacitor Cstd. The first switching circuit 112d includes ninth and tenth transistors M94 and M104. The second switching circuit 113d includes 11<sup>th</sup> and 12<sup>th</sup> transistors M114 and M124. Each transistor includes a source, a drain, and a gate. The capacitor Cstd includes a first electrode and a second electrode.

Since the drains and the sources of the first to twelfth transistors M14 to M124 have no physical difference, each source and drain may be referred to as a first electrode and a second electrode.

The drain of the first transistor M14 is connected with a first node A4, the source of the first transistor M14 is connected with a second node B4, and the gate of the first transistor M14 is connected with a third node C4 so that a current flows from the second node B4 to the first node A4 in accordance with a voltage of the third node C4.

The source of the second transistor M24 is connected with a data line Dm, the drain of the second transistor M24 is connected with the second node B4, and the gate of the second transistor M24 is connected with a first scan line Sn so that the second transistor M24 performs a switching operation in accordance with a first scan signal sn transmitted through the first scan line Sn to selectively transmit a data signal transmitted through the data line Dm to the second node B4.

The source of the third transistor M34 is connected with the first node A4, the drain of the third transistor M34 is connected with the third node C4, and the gate of the third transistor M34 is connected with the first scan line Sn so that the potential of the first node A4 is made equal to the potential of the third node C4 in accordance with the first scan signal sn transmitted through the first scan line Sn to have an electric current flow through the first transistor M14. Therefore, the first transistor M14 serves as a diode.

The source and gate of the fourth transistor M44 are connected with a second scan line Sn-1 and the drain of the fourth transistor M44 is connected with the third node C4 so that the fourth transistor M44 applies an initializing signal to the third node C4. The initializing signal is a second scan signal sn-1 input to select the row that precedes by one row the row to which the first scan signal sn is input to select, and is received through the second scan line Sn-1. That is, the second scan line Sn-1 refers to the scan line connected with the row that precedes the row to which the first scan line Sn is connected by one row.

The source of the fifth transistor M54 is connected with a pixel power source Vdd, the drain of the fifth transistor M54 is connected with the second node B4, and the gate of the fifth transistor M54 is connected with a first emission control line E1n so that the fifth transistor M54 selectively applies a pixel power of the pixel power source Vdd to the second node B4 in accordance with a first emission control signal  $e1n$  transmitted through the first emission control line E1n.

The source of the sixth transistor M64 is connected with the pixel power source Vdd, the drain of the sixth transistor M64 is connected with the second node B4, and the gate of the sixth transistor M64 is connected with a second emission control

line E<sub>2n</sub> so that the sixth transistor M<sub>64</sub> selectively applies the pixel power of the pixel power source Vdd to the second node B<sub>4</sub> in accordance with a second emission control signal e<sub>2n</sub> transmitted through the second emission control line E<sub>2n</sub>.

The source of the seventh transistor M<sub>74</sub> is connected with the pixel power source Vdd, the drain of the seventh transistor M<sub>74</sub> is connected with the second node B<sub>4</sub>, and the gate of the seventh transistor M<sub>74</sub> is connected with a third emission control line E<sub>3n</sub> so that the seventh transistor M<sub>74</sub> selectively applies the pixel power of the pixel power source Vdd to the second node B<sub>4</sub> in accordance with a third emission control signal e<sub>3n</sub> transmitted through the third emission control line E<sub>3n</sub>.

The source of the eighth transistor M<sub>84</sub> is connected with the pixel power source Vdd, the drain of the eighth transistor M<sub>84</sub> is connected with the second node B<sub>4</sub>, and the gate of the eighth transistor M<sub>84</sub> is connected with a fourth emission control line E<sub>4n</sub> so that the eighth transistor M<sub>84</sub> selectively applies the pixel power of the pixel power source Vdd to the second node B<sub>4</sub> in accordance with a fourth emission control signal e<sub>4n</sub> transmitted through the fourth emission control line E<sub>4n</sub>.

The source of the ninth transistor M<sub>94</sub> is connected with the first node A<sub>4</sub>, the drain of the ninth transistor M<sub>94</sub> is connected with the first OLED OLED<sub>14</sub>, and the gate of the ninth transistor M<sub>94</sub> is connected with the first emission control line E<sub>1n</sub> so that the current that flows through the first node A<sub>4</sub> flows to the first OLED OLED<sub>14</sub> in accordance with the first emission control signal e<sub>1n</sub> transmitted through the first emission control line E<sub>1n</sub> to emit light from the first OLED OLED<sub>14</sub>.

The source of the tenth transistor M<sub>104</sub> is connected with the first node A<sub>4</sub>, the drain of the tenth transistor M<sub>104</sub> is connected with the second OLED OLED<sub>24</sub>, and the gate of the tenth transistor M<sub>104</sub> is connected with the second emission control line E<sub>2n</sub> so that the current that flows through the first node A<sub>4</sub> flows to the second OLED OLED<sub>24</sub> in accordance with the second emission control signal e<sub>2n</sub> transmitted through the second emission control line E<sub>2n</sub> to emit light from the second OLED OLED<sub>24</sub>.

The source of the 11<sup>th</sup> transistor M<sub>114</sub> is connected with the first node A<sub>4</sub>, the drain of the 11<sup>th</sup> transistor M<sub>114</sub> is connected with the third OLED OLED<sub>34</sub>, and the gate of the 11<sup>th</sup> transistor M<sub>114</sub> is connected with the third emission control line E<sub>3n</sub> so that the current that flows through the first node A<sub>4</sub> flows to the third OLED OLED<sub>34</sub> in accordance with the third emission control signal e<sub>3n</sub> transmitted through the third emission control line E<sub>3n</sub> to emit light from the third OLED OLED<sub>34</sub>.

The source of the 12<sup>th</sup> transistor M<sub>124</sub> is connected with the first node A<sub>4</sub>, the drain of the 12<sup>th</sup> transistor M<sub>124</sub> is connected with the fourth OLED OLED<sub>44</sub>, and the gate of the 12<sup>th</sup> transistor M<sub>124</sub> is connected with the fourth emission control line E<sub>4n</sub> so that the current that flows through the fourth node A<sub>4</sub> flows to the fourth OLED OLED<sub>44</sub> in accordance with the fourth emission control signal e<sub>4n</sub> transmitted through the fourth emission line E<sub>4n</sub> to emit light from the fourth OLED OLED<sub>44</sub>.

The first electrode of the capacitor Cstd is connected with the pixel power source Vdd and the second electrode of the capacitor Cstd is connected with the third node C<sub>4</sub> so that the capacitor Cstd is initialized by the initializing signal transmitted to the third node C<sub>4</sub> through the fourth transistor M<sub>44</sub>, and the voltage corresponding to the data signal is stored by the capacitor Cstd and then transmitted to the third node C<sub>4</sub>. Therefore, the gate voltage of the first transistor M<sub>14</sub> is maintained for a predetermined time.

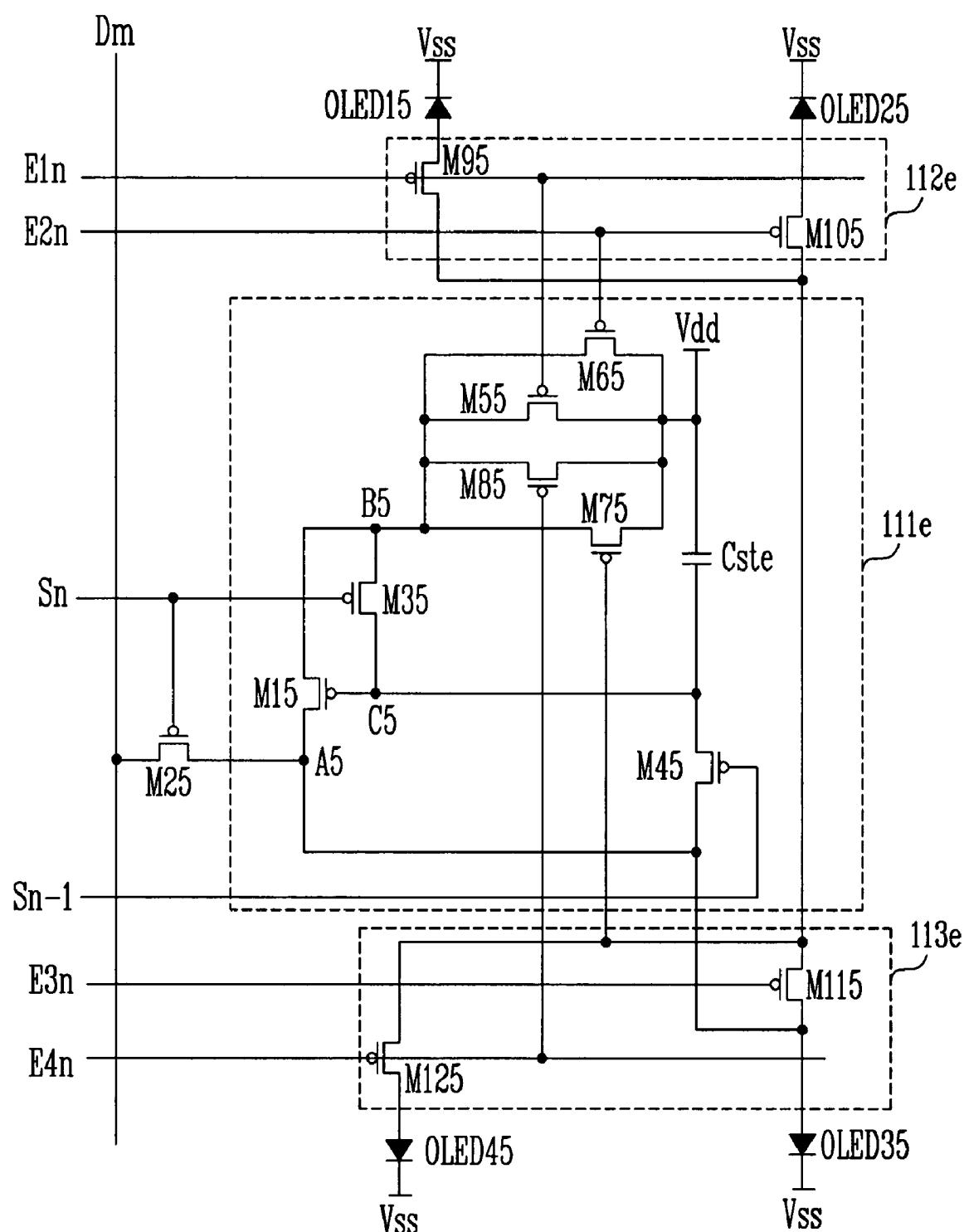

FIG. 14 is a circuit diagram illustrating a second embodiment of a pixel of the light emitting display of FIG. 10. Referring to FIG. 14, the pixel includes four OLEDs and a pixel circuit (e.g., the pixel circuit 110c). The four OLEDs 5 OLED<sub>15</sub>, OLED<sub>25</sub>, OLED<sub>35</sub>, and OLED<sub>45</sub> are connected with one pixel circuit. The pixel circuit (e.g., the pixel circuit 110c) includes a driving circuit 111e, a first switching circuit 112e, and a second switching circuit 113e.

The driving circuit 111e includes first to eighth transistors 10 M<sub>15</sub> to M<sub>85</sub> and a capacitor Cste. The first switching circuit 112e includes ninth and tenth transistors M<sub>95</sub> and M<sub>105</sub>. The second switching circuit 113e includes 11<sup>th</sup> and 12<sup>th</sup> transistors M<sub>115</sub> and M<sub>125</sub>. Each transistor includes a source, a drain, and a gate. The capacitor Cste includes a first electrode and a second electrode.

Since the drains and sources of the first to 12<sup>th</sup> transistors 15 M<sub>15</sub> to M<sub>125</sub> have no physical difference, each source and drain may be referred to as a first electrode and a second electrode.

20 The drain of the first transistor M<sub>15</sub> is connected with a first node A<sub>5</sub>, the source of the first transistor M<sub>15</sub> is connected with a second node B<sub>5</sub>, and the gate of the first transistor M<sub>15</sub> is connected with a third node C<sub>5</sub> so that a current flows from the second node B<sub>5</sub> to the first node A<sub>5</sub> in accordance with a voltage of the third node C<sub>5</sub>.

25 The source of the second transistor M<sub>25</sub> is connected with the data line Dm, the drain of the second transistor M<sub>25</sub> is connected with the first node A<sub>5</sub>, and the gate of the second transistor M<sub>25</sub> is connected with a first scan line Sn so that the second transistor M<sub>25</sub> performs a switching operation in accordance with a first scan signal sn transmitted through the first scan signal Sn to selectively transmit a data signal transmitted through a data line Dm to the first node A<sub>5</sub>.

30 The source of the third transistor M<sub>35</sub> is connected with the second node B<sub>5</sub>, the drain of the third transistor M<sub>35</sub> is connected with the third node C<sub>5</sub>, and the gate of the third transistor M<sub>35</sub> is connected with the first scan line Sn so that the potential of the second node B<sub>5</sub> is made equal to the potential of the third node C<sub>5</sub> in accordance with the first scan 35 signal sn transmitted through the first scan line Sn to have an electric current flow through the first transistor M<sub>15</sub>. Therefore, the first transistor M<sub>15</sub> serves as a diode.

35 The source of the fourth transistor M<sub>45</sub> is connected with an anode electrode of an OLED (e.g., the OLED 35), the drain 40 of the fourth transistor M<sub>45</sub> is connected with the third node C<sub>5</sub>, and the gate of the fourth transistor M<sub>45</sub> is connected with a second scan line Sn-1 so that the fourth transistor M<sub>45</sub> applies a voltage when no current flows to the first to fourth OLEDs OLED<sub>15</sub> to OLED<sub>45</sub> to the third node C<sub>5</sub> in accordance with a second scan signal sn-1. At this time, the voltage transmitted to the third node C<sub>5</sub> in accordance with the second scan signal sn-1 is used as an initializing signal for initializing the capacitor Cste.

45 The source of the fifth transistor M<sub>55</sub> is connected with a pixel power source Vdd, the drain of the fifth transistor M<sub>55</sub> is connected with the second node B<sub>5</sub>, and the gate of the fifth transistor M<sub>55</sub> is connected with a first emission control line E<sub>1n</sub> so that the fifth transistor M<sub>55</sub> selectively applies a pixel power of the pixel power source Vdd to the second node B<sub>5</sub> in accordance with a first emission control signal e<sub>1n</sub> transmitted through the first emission control line E<sub>1n</sub>.

50 The source of the sixth transistor M<sub>65</sub> is connected with the pixel power source Vdd, the drain of the sixth transistor M<sub>65</sub> is connected with the second node B<sub>5</sub>, and the gate of the sixth transistor M<sub>65</sub> is connected with a second emission control line E<sub>2n</sub> so that the sixth transistor M<sub>65</sub> selectively applies the pixel power of the pixel power source Vdd to the second

node B<sub>5</sub> in accordance with a second emission control signal e<sub>2n</sub> transmitted through the second emission control line E<sub>2n</sub>.

The source of the seventh transistor M<sub>75</sub> is connected with the pixel power source line V<sub>dd</sub>, the drain of the seventh transistor M<sub>75</sub> is connected with the second node B<sub>5</sub>, and the gate of the seventh transistor M<sub>75</sub> is connected with a third emission control line E<sub>3n</sub> so that the seventh transistor M<sub>75</sub> selectively applies the pixel power of the pixel power source V<sub>dd</sub> to the second node B<sub>5</sub> in accordance with a third emission control signal e<sub>3n</sub> transmitted through the third emission control line E<sub>3n</sub>.

The source of the eighth transistor M<sub>85</sub> is connected with the pixel power source V<sub>dd</sub>, the drain of the eighth transistor M<sub>85</sub> is connected with the second node B<sub>5</sub>, and the gate of the eighth transistor M<sub>85</sub> is connected with a fourth emission control line E<sub>4n</sub> so that the eighth transistor M<sub>85</sub> selectively applies the pixel power source to the second node B<sub>5</sub> in accordance with a fourth emission control signal e<sub>4n</sub> transmitted through the fourth emission control line E<sub>4n</sub>.

The source of the ninth transistor M<sub>95</sub> is connected with the first node A<sub>5</sub>, the drain of the ninth transistor M<sub>95</sub> is connected with the first OLED OLED1<sub>5</sub>, and the gate of the ninth transistor M<sub>95</sub> is connected with the first emission control line E<sub>1n</sub> so that the current that flows through the first node A<sub>5</sub> flows to the first OLED OLED1<sub>5</sub> in accordance with the first emission control signal e<sub>1n</sub> transmitted through the first emission control line E<sub>1n</sub> to emit light from the first OLED OLED1<sub>5</sub>.

The source of the tenth transistor M<sub>105</sub> is connected with the first node A<sub>5</sub>, the drain of the tenth transistor M<sub>105</sub> is connected with the second OLED OLED2<sub>5</sub>, and the gate of the tenth transistor M<sub>105</sub> is connected with the second emission control line E<sub>2n</sub> so that the current that flows through the first node A<sub>5</sub> flows to the second OLED OLED2<sub>5</sub> in accordance with the second emission control signal e<sub>2n</sub> transmitted through the second emission control line E<sub>2n</sub> to emit light from the second OLED OLED2<sub>5</sub>.

The source of the 11<sup>th</sup> transistor M<sub>15</sub> is connected with the first node A<sub>5</sub>, the drain of the 11<sup>th</sup> transistor M<sub>115</sub> is connected with the third OLED OLED3<sub>5</sub>, and the gate of the 11<sup>th</sup> transistor M<sub>115</sub> is connected with the third emission control line E<sub>3n</sub> so that the current that flows through the first node A<sub>5</sub> flows to the third OLED OLED3<sub>5</sub> in accordance with the third emission control signal e<sub>3n</sub> transmitted through the third emission control line E<sub>3n</sub> to emit light from the third OLED OLED3<sub>5</sub>.

The source of the 12<sup>th</sup> transistor M<sub>125</sub> is connected with the first node A<sub>5</sub>, the drain of the 12<sup>th</sup> transistor M<sub>125</sub> is connected with the fourth OLED OLED4<sub>5</sub>, and the gate of the 12<sup>th</sup> transistor M<sub>125</sub> is connected with the fourth emission control line E<sub>4n</sub> so that the current that flows through the fourth node A<sub>5</sub> flows to the fourth OLED OLED4<sub>5</sub> in accordance with the fourth emission control signal e<sub>4n</sub> transmitted through the fourth emission control line E<sub>4n</sub> to emit light from the fourth OLED OLED4<sub>5</sub>.

The first electrode of the capacitor C<sub>ste</sub> is connected with the pixel power source V<sub>dd</sub>, and the second electrode of the capacitor C<sub>ste</sub> is connected with the third node C<sub>5</sub> so that the capacitor C<sub>ste</sub> is initialized by the initializing signal transmitted to the third node C<sub>5</sub> through the fourth transistor M<sub>45</sub> and so that the voltage corresponding to the data signal is stored by the capacitor C<sub>ste</sub> and then transmitted to the third node C<sub>5</sub>. Therefore, the gate voltage of the first transistor M<sub>15</sub> is maintained for a predetermined time.

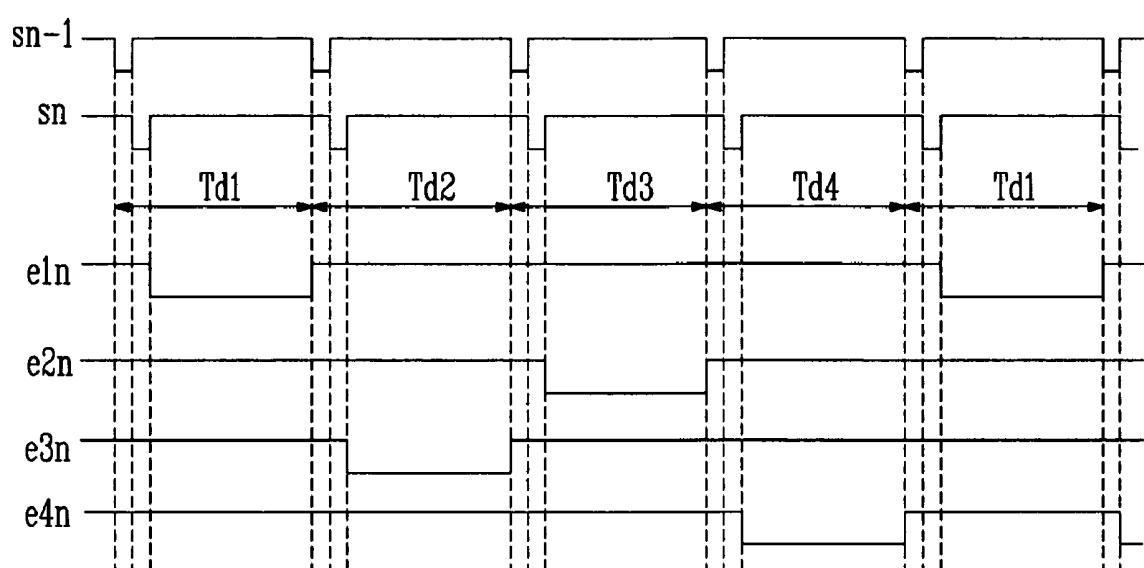

FIG. 15 illustrates waveforms of signals transmitted to the light emitting display that uses the pixels illustrated in FIGS. 13 and 14. Referring to FIG. 15, the pixel is operated by first

and second scan signals sn and sn-1, a data signal, and first, second, third, and fourth emission control signals e<sub>1n</sub>, e<sub>2n</sub>, e<sub>3n</sub>, and e<sub>4n</sub>. The first and second scan signals sn and sn-1 and the first to fourth emission control signals e<sub>1n</sub> to e<sub>4n</sub> are periodical signals having first to fourth periods Td1 to Td4.

In the first period Td1, the first emission control signal e<sub>1n</sub> is in a low level. In the second period Td2, the third emission control signal e<sub>3n</sub> is in the low level. In the third period Td3, the second emission control signal e<sub>2n</sub> is in the low level. In the fourth period Td4, the fourth emission control signal e<sub>4n</sub> is in the low level. The second scan signal sn-1 is the scan signal for selecting a line that precedes the line to which the first scan signal sn is input to select. The first scan signal sn and the second scan signal sn-1 are sequentially in the low level for a moment at the starting point of each period.

In the first period Td1, a fourth transistor M<sub>4</sub> (e.g., M<sub>44</sub> and M<sub>45</sub>) is turned on by the second scan signal sn-1, and an initializing signal is transmitted to the capacitor C<sub>st</sub> (e.g., C<sub>std</sub> or C<sub>ste</sub>) through the fourth transistor M<sub>4</sub> to initialize the capacitor C<sub>st</sub>. A second transistor M<sub>2</sub> (e.g., M<sub>24</sub> or M<sub>25</sub>) and a third transistor M<sub>3</sub> (e.g., M<sub>34</sub> and M<sub>35</sub>) are turned on by the first scan signal sn so that the potential of a first node A<sub>4</sub> or a second node B<sub>5</sub> is made equal to the potential of a third node C (e.g., C<sub>4</sub> or C<sub>5</sub>) to have an electric current flow through a first transistor M<sub>1</sub> (e.g., M<sub>14</sub> or M<sub>15</sub>). Therefore, the first transistor M<sub>1</sub> (e.g., M<sub>14</sub> or M<sub>15</sub>) is connected like a diode. The data signal is applied to a second node B<sub>4</sub> or a second node A<sub>5</sub> through the second transistor M<sub>2</sub> (e.g., M<sub>24</sub> or M<sub>25</sub>). Therefore, the data signal is transmitted to a second electrode of the capacitor C<sub>st</sub> (e.g., C<sub>std</sub> or C<sub>ste</sub>) through the second transistor M<sub>2</sub> (e.g., M<sub>24</sub> or M<sub>25</sub>), the first transistor M<sub>1</sub> (e.g., or M<sub>14</sub> or M<sub>15</sub>), and the third transistor M<sub>3</sub> (e.g., M<sub>34</sub> or M<sub>35</sub>) so that the voltage corresponding to difference between the data signal and the threshold voltage is transmitted to the second electrode of the capacitor C<sub>st</sub> (e.g., C<sub>std</sub> or C<sub>ste</sub>).

After the first scan signal sn is transited to the high level, when the first emission control signal e<sub>1n</sub> is transited to the low level and is maintained in the low level for a predetermined time, a fifth transistor M<sub>5</sub> (e.g., M<sub>54</sub> or M<sub>55</sub>) and a ninth transistor M<sub>9</sub> (e.g., M<sub>94</sub> or M<sub>95</sub>) are turned on by the first emission control signal e<sub>1n</sub> so that the voltage corresponding to the EQUATION 1 is applied between the gate and the source of the first transistor M<sub>1</sub> (e.g., M<sub>14</sub> or M<sub>15</sub>).

The ninth transistor M<sub>9</sub> (e.g., M<sub>94</sub> or M<sub>95</sub>) is turned on so that the current corresponding to the EQUATION 2 flows to an OLED OLED1 (E.G., OLED1<sub>4</sub> or OLED1<sub>5</sub>).

Therefore, referring now to FIGS. 13 and 14 and EQUATION 2, the current flows to the first OLEDs OLED1<sub>4</sub> and OLED1<sub>5</sub> regardless of the threshold voltages of the first transistors M<sub>14</sub> and M<sub>15</sub>.

In the second period Td2, the voltage value corresponding to the difference between the pixel power source and the data signal is stored in the capacitor C<sub>st</sub> (e.g., C<sub>std</sub> or C<sub>ste</sub>) by the first and second scan signals sn and sn-1, and the data signal and the voltage corresponding to the EQUATION 1 are transmitted to the first transistor M<sub>1</sub> (e.g., M<sub>14</sub> or M<sub>15</sub>). A seventh transistor M<sub>7</sub> (e.g., M<sub>74</sub> or M<sub>75</sub>) and an 11<sup>th</sup> transistor M<sub>11</sub> (e.g., M<sub>114</sub> or M<sub>115</sub>) are turned on by a third emission control signal e<sub>3n</sub> and a current corresponding to the EQUATION 2 flows through a third OLED OLED3 (e.g., OLED3<sub>4</sub> or OLED3<sub>5</sub>).

In the third and fourth periods Td3 and Td4, currents are generated substantially the same as in the first and second periods Td1 and Td2. That is, in the third period Td3, a sixth transistor M<sub>6</sub> (e.g., M<sub>64</sub> or M<sub>65</sub>) is turned on by a second emission control signal e<sub>2n</sub> so that a current flows to a second

OLED OLED2 (e.g., OLED24 or OLED25). In the fourth period Td4, an eighth transistor M8 (e.g., M84 or M85) and an 12<sup>th</sup> transistor M12 (e.g., M124 or M125) are turned on by a fourth emission control signal e4n so that a current flows to a fourth OLED OLED4 (e.g., OLED44 or OLED45).

Therefore, the first to fourth OLEDs OLED1 to OLED4 (e.g., OLED14 to OLED44 or OLED15 to OLED45) sequentially emit light in the order described above.

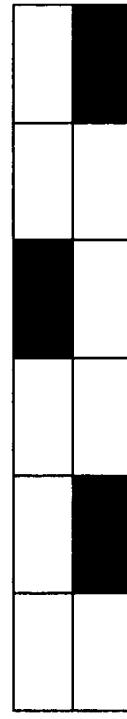

FIGS. 16A to 16D illustrate emission processes of the light emitting display of FIG. 9. In the image display unit 100b, three pixel circuits are vertically arranged so that twelve OLEDs are arranged in the form of a 2x6 matrix. A top pixel circuit, a central pixel circuit, and a bottom pixel circuit may be referred to as a first pixel circuit, a second pixel circuit, and a third pixel circuit. Referring to FIGS. 16A to 16D, since all four OLEDs are connected with one pixel circuit to sequentially emit light for one frame, one frame may be divided into four sub-fields.

As first OLED OLED13 and the third OLED OLED33 connected with one pixel circuit among the two pixel circuits adjacent to one data line receive a red data signal R to emit red light, and the second OLED OLED23 and the fourth OLED OLED43 receive a green data signal G to emit green light, the first OLED OLED13 and the third OLED OLED33 connected with the other pixel circuit among the two circuits receive the green data signal G to emit green light, and the second OLED OLED23 and the fourth OLED OLED43 receive the red data signal R to emit red light. The red data and the green data are alternately transmitted through one data line.

FIG. 16A illustrates the first sub-field among the four sub-fields. As illustrated in FIG. 16A, the first pixel circuit and the third pixel circuit emit red light through the first OLED OLED13 receiving the red data and the second pixel circuit emits green light through the first OLED OLED13 receiving the green data so that the red and green light components are simultaneously emitted.

In FIG. 16B that illustrates the second sub-field, the first pixel circuit and the third pixel circuit emit green light through the third OLED OLED33 receiving the green data and the second pixel circuit emits red light through the third OLED OLED33 receiving the red data so that the red and green light components are simultaneously emitted. Also, in the third and fourth sub-fields illustrated in FIGS. 16C and 16D, the red and green light components are simultaneously emitted.